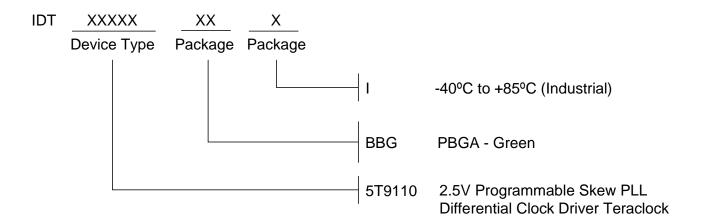

## 2.5V PROGRAMMABLE SKEW PLL DIFFERENTIAL CLOCK DRIVER TERACLOCK™

IDT5T9110

## PRODUCT DISCONTINUATION NOTICE - LAST TIME BUY EXPIRES ON OCTOBER 28, 2014

## FEATURES:

- 2.5 VDD

- · 6 pairs of programmable skew outputs

- · Low skew: 100ps all outputs

- Selectable positive or negative edge synchronization

- · Tolerant to spread spectrum input clock

- Synchronous output enable

- Selectable reference input

- Input frequency: 4.17MHz to 250MHz

- Output frequency: 12.5MHz to 250MHz

- 1.8V / 2.5V LVTTL: up to 250MHz

- · HSTL / eHSTL: up to 250MHz

- Hot insertable and over-voltage tolerant inputs

- 3-level inputs for skew control

- 3-level inputs for selectable interface

- 3-level inputs for divide selection multiply/divide ratios of (1-6, 8, 10, 12) / (2, 4)

- · Selectable HSTL, eHSTL, 1.8V/2.5V LVTTL, or LVEPECL input interface

- · Selectable differential or single-ended inputs and six differential outputs

- PLL bypass for DC testing

- External differential feedback, internal loop filter

- Low Jitter: <75ps cycle-to-cycle

- Power-down mode

- · Lock indicator

- Available in BGA package

- use replacement parts: 873995AYLF & 873996AYLF

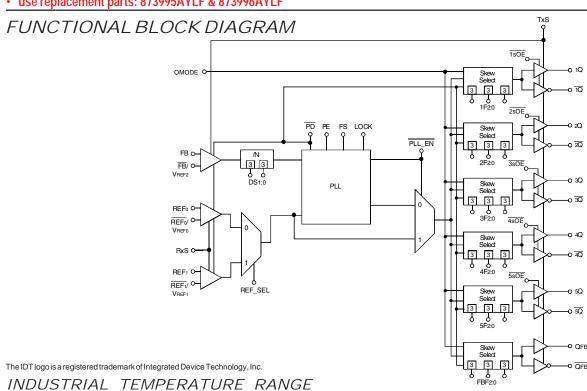

#### DESCRIPTION:

The IDT5T9110 is a 2.5V PLL differential clock driver intended for high performance computing and data-communications applications. A key feature of the programmable skew is the ability of outputs to lead or lag the REF input signal. The IDT5T9110 has six differential programmable skew outputs in six banks, including a dedicated differential feedback. Skew is controlled by 3-level input signals that may be hard-wired to appropriate high-mid-low levels. The redundant input capability allows for a smooth change over to a secondary clock source when the primary clock source is absent.

The feedback bank allows divide-by-functionality from 1 to 12 through the use of the DS[1:0] inputs. This provides the user with frequency multiplication 1 to 12 without using divided outputs for feedback. Each output bank also allows for a divide-by functionality of 2 or 4.

The IDT5T9110 features a user-selectable, single-ended or differential input to six differential outputs. The differential clock driver also acts as a translator from a differential HSTL, eHSTL, 1.8V/2.5V LVTTL, LVEPECL, or single-ended 1.8V/2.5V LVTTL input to HSTL, eHSTL, or 1.8V/2.5V LVTTL outputs. Selectable interface is controlled by 3-level input signals that may be hard-wired to appropriate high-mid-low levels. The differential outputs can be synchronously enabled/disabled.

Furthermore, when PE is held high, all the outputs are synchronized with the positive edge of the REF clock input. When PE is held low, all the outputs are synchronized with the negative edge of REF.

MAY 2013

## **PIN CONFIGURATION**

|   | 1           | 2               | 3               | 4    | 5               | 6   | 7   | 8   | 9          | 10   | 11   | 12             |   |

|---|-------------|-----------------|-----------------|------|-----------------|-----|-----|-----|------------|------|------|----------------|---|

| Α | VDD         | 1F2             | 1sOE            | 1Q   | 1Q              | GND | GND | 2Q  | 2Q         | 2sOE | 2F2  | VDDQ           | Α |

| В | VDD         | V <sub>DD</sub> | VDD             | 1Fo  | 1F <sub>1</sub> | GND | GND | 2F1 | 2F0        | VDDQ | VDDQ | 3F2            | В |

| С | OMODE       | VDD             | VDD             | VDD  | GND             | GND | GND | GND | VDDQ       | VDDQ | VDDQ | 3sOE           | С |

| D | REF_<br>SEL | VDD             | VDD             | VDD  | GND             | GND | GND | GND | VDDQ       | VDDQ | 3Fo  | зQ             | D |

| E | REF1        | REF1<br>/VREF1  | NC              | VDD  | GND             | GND | GND | GND | VDDQ       | VDDQ | 3F1  | <del>3</del> Q | Ε |

| F | REF0        | REF0<br>/VREF0  | V <sub>DD</sub> | VDD  | GND             | GND | GND | GND | VDDQ       | VDDQ | VDDQ | VDDQ           | F |

| G | FB          | FB<br>/VREF2    | VDD             | VDD  | GND             | GND | GND | GND | VDDQ       | VDDQ | VDDQ | VDDQ           | G |

| Н | PD          | PLL_<br>EN      | PE              | VDD  | GND             | GND | GND | GND | VDDQ       | VDDQ | 4F1  | 4Q             | Н |

| J | RxS         | TxS             | VDD             | VDD  | GND             | GND | GND | GND | VDDQ       | VDDQ | 4F0  | 4Q             | J |

| K | LOCK        | VDD             | VDD             | VDD  | GND             | GND | GND | GND | VDDQ       | VDDQ | VDDQ | 4sOE           | K |

| L | VDD         | VDD             | FS              | FBF0 | FBF1            | GND | GND | 5F1 | 5Fo        | VDDQ | VDDQ | 4F2            | L |

| М | DS1         | DS <sub>0</sub> | FBF2            | QFB  | QFB             | GND | GND | 5Q  | 5 <b>Q</b> | 5sOE | 5F2  | VDDQ           | М |

|   | 1           | 2               | 3               | 4    | 5               | 6   | 7   | 8   | 9          | 10   | 11   | 12             |   |

### 2.5V PROGRAMMABLE SKEW PLL DIFFERENTIAL CLOCK DRIVER TERACLOCK

## ABSOLUTE MAXIMUM RATINGS(1)

| Symbol    | Description                         | Max               | Unit |

|-----------|-------------------------------------|-------------------|------|

| VDDQ, VDD | Power Supply Voltage <sup>(2)</sup> | -0.5 to +3.6      | V    |

| Vı        | Input Voltage                       | -0.5 to +3.6      | V    |

| Vo        | Output Voltage                      | -0.5 to VDDQ +0.5 | V    |

| VREF      | Reference Voltage <sup>(3)</sup>    | -0.5 to +3.6      | V    |

| TJ        | Junction Temperature                | 150               | °C   |

| Tstg      | Storage Temperature                 | -65 to +165       | °C   |

#### NOTES:

- 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- VDDQ and VDD internally operate independently. No power sequencing requirements need to be met.

- 3. Not to exceed 3.6V.

## CAPACITANCE(TA = +25°C, f = 1MHz, Vin = 0V)

| Paramete | er | Description        | Min. | Тур. | Max. | Unit |

|----------|----|--------------------|------|------|------|------|

| CIN      |    | Input Capacitance  | 2.5  | 3    | 3.5  | pF   |

| Соит     |    | Output Capacitance | T -  | 6.3  | 7    | pF   |

## NOTE:

1. Capacitance applies to all inputs except RxS, TxS, nF[2:0], FBF[2:0].and DS[1:0].

## RECOMMENDED OPERATING RANGE

| Symbol                         | Description                                              | Min. | Тур.   | Max. | Unit |

|--------------------------------|----------------------------------------------------------|------|--------|------|------|

| TA                             | Ambient Operating Temperature                            | -40  | +25    | +85  | °C   |

| V <sub>DD</sub> <sup>(1)</sup> | Internal Power Supply Voltage                            | 2.3  | 2.5    | 2.7  | V    |

|                                | HSTL Output Power Supply Voltage                         | 1.4  | 1.5    | 1.6  | V    |

| VDDQ <sup>(1)</sup>            | Extended HSTL and 1.8V LVTTL Output Power Supply Voltage | 1.65 | 1.8    | 1.95 | V    |

|                                | 2.5V LVTTL Output Power Supply Voltage                   |      | Vdd    |      | V    |

| VT                             | Termination Voltage                                      |      | VDDQ/2 |      | V    |

#### NOTE:

## **PIN DESCRIPTION**

| Symbol                 | I/O | Туре                      | Description                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|------------------------|-----|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| REF[1:0]               | I   | Adjustable <sup>(1)</sup> | Clock input. REF[1:0] is the "true" side of the differential clock input. If operating in single-ended mode, REF[1:0] is the clock input.                                                                                                                                                                                                                                   |  |  |

| REF[1:0]/<br>VREF[1:0] | I   | Adjustable <sup>(1)</sup> | Complementary clock input. $\overline{REF}$ [1:0]/VREF[1:0] is the "complementary" side of REF[1:0] if the input is in differential mode. If operating in single-ended mode, $\overline{REF}$ [1:0]/VREF[1:0] is left floating. For single-ended operation in differential mode, $\overline{REF}$ [1:0]/VREF[1:0] should be set to the desired toggle voltage for REF[1:0]: |  |  |

|                        |     |                           | 2.5V LVTTL VREF = 1250mV (SSTL2 compatible)                                                                                                                                                                                                                                                                                                                                 |  |  |

|                        |     |                           | 1.8V LVTTL, eHSTL VREF = 900mV                                                                                                                                                                                                                                                                                                                                              |  |  |

|                        |     |                           | HSTL VREF = 750mV                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                        |     |                           | LVEPECL VREF = 1082mV                                                                                                                                                                                                                                                                                                                                                       |  |  |

| FB                     | I   | Adjustable <sup>(1)</sup> | Clock input. FB is the "true" side of the differential feedback clock input. If operating in single-ended mode, FB is the differential feedback clock input.                                                                                                                                                                                                                |  |  |

| FB/VREF2               | I   | Adjustable <sup>(1)</sup> | Complementary feedback clock input. FB/VREF2 is the "complementary" side of FB if the input is in differential mode. If operating in single-ended mode, FB/VREF2 is left floating. For single-ended operation in differential mode, FB/VREF2 should be set to the desired toggle voltage for FB:                                                                            |  |  |

|                        |     |                           | 2.5V LVTTL VREF = 1250mV (SSTL2 compatible)                                                                                                                                                                                                                                                                                                                                 |  |  |

|                        |     |                           | 1.8V LVTTL, eHSTL VREF = 900mV                                                                                                                                                                                                                                                                                                                                              |  |  |

|                        |     |                           | HSTL VREF = 750mV                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                        |     |                           | LVEPECL VREF = 1082mV                                                                                                                                                                                                                                                                                                                                                       |  |  |

#### NOTE:

1. Inputs are capable of translating the following interface standards. User can select between:

Single-ended 2.5V LVTTL levels

Single-ended 1.8V LVTTL levels

or

Differential 2.5V/1.8V LVTTL levels

Differential HSTL and eHSTL levels

Differential LVEPECL levels

<sup>1.</sup> All power supplies should operate in tandem. If VDD or VDDQ is at maximum, then VDDQ or VDD (respectively) should be at maximum, and vice-versa.

## PIN DESCRIPTION, CONTINUED

| Symbol   | I/O | Туре                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-----|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REF_SEL  | I   | LVTTL <sup>(1)</sup>      | Reference clock select. When LOW, selects REFo and REFo/VREFO. When HIGH, selects REF1 and REF1/VREF1.                                                                                                                                                                                                                                                                                                                                                                                                               |

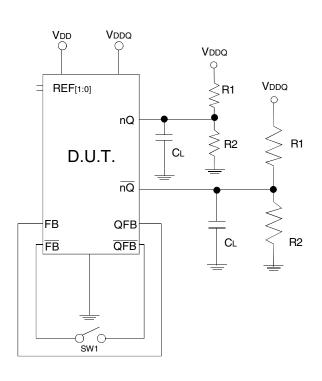

| nsOE     | l   | LVTTL <sup>(1)</sup>      | Synchronous output enable. When $\overline{\text{nsOE}}$ is HIGH, $\overline{\text{nQ}}$ are synchronously stopped. OMODE selects whether the outputs are gated LOW/HIGH or tri-stated. When OMODE is HIGH, PE determines the level at which the outputs stop. When PE is LOW/HIGH, the $\overline{\text{nQ}}$ is stopped in a HIGH/LOW state, while the $\overline{\text{nQ}}$ is stopped at a LOW/HIGH state. When OMODE is LOW, the outputs are tristated. Set $\overline{\text{nsOE}}$ LOW for normal operation. |

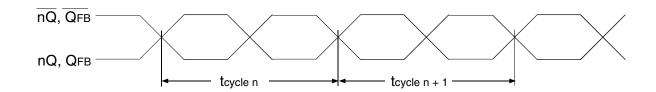

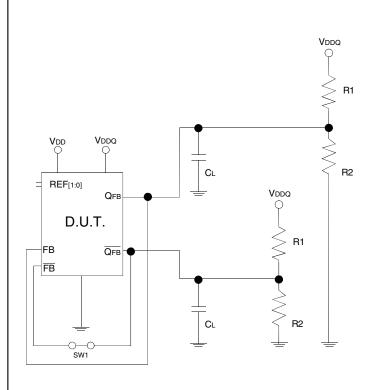

| QFB      | 0   | Adjustable <sup>(2)</sup> | Feedback clock output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| QFB      | 0   | Adjustable <sup>(2)</sup> | Complementary feedback clock output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| nQ       | 0   | Adjustable <sup>(2)</sup> | Clockoutputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| nQ       | 0   | Adjustable <sup>(2)</sup> | Complementary clock outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RxS      | - 1 | 3-Level <sup>(3)</sup>    | Selects single-ended 2.5V LVTTL (HIGH), 1.8V LVTTL (MID) REF clock input or differential (LOW) REF clock input                                                                                                                                                                                                                                                                                                                                                                                                       |

| TxS      | I   | 3-Level <sup>(3)</sup>    | Sets the drive strength of the output drivers and feedback inputs to be 2.5V LVTTL (HIGH), 1.8V LVTTL (MID) or eHSTL/HSTL (LOW) compatible. Used in conjuction with VDDQ to set the interface levels.                                                                                                                                                                                                                                                                                                                |

| PE       | I   | LVTTL <sup>(1)</sup>      | Selectable positive or negative edge control. When LOW/HIGH the outputs are synchronized with the negative/positive edge of the reference clock (has internal pull-up).                                                                                                                                                                                                                                                                                                                                              |

| nF[2:0]  | I   | 3-Level <sup>(3)</sup>    | 3-level inputs for selecting 1 of 18 skew taps or frequency functions (See Control Summary table)                                                                                                                                                                                                                                                                                                                                                                                                                    |

| FBF[2:0] | I   | 3-Level <sup>(3)</sup>    | 3-level inputs for selecting 1 of 18 skew taps or frequency functions (See Control Summary table)                                                                                                                                                                                                                                                                                                                                                                                                                    |

| FS       | I   | LVTTL                     | Selects appropriate oscillator circuit based on anticipated frequency range (See Programmable Skew Range table)                                                                                                                                                                                                                                                                                                                                                                                                      |

| DS[1:0]  | I   | 3-Level <sup>(3)</sup>    | 3-level inputs for feedback input divider selection (See Divide Selection table)                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PLL_EN   | I   | LVTTL <sup>(1)</sup>      | $PLL enable/disable control. \ Set LOW for normal operation. \ When \overline{PLL\_EN} is HIGH, the PLL is disabled and REF \cite{Control} goes to all outputs.$                                                                                                                                                                                                                                                                                                                                                     |

| PD       | I   | LVTTL <sup>(1)</sup>      | Power down control. When $\overline{PD}$ is LOW, the inputs are disabled and internal switching is stopped. OMODE selects whether the outputs are gated LOW/HIGH or tri-stated. When OMODE is HIGH, PE determines the level at which the outputs stop. When PE is LOW/HIGH, the nQ and QFB are stopped in a HIGH/LOW state, while the $\overline{nQ}$ and $\overline{QFB}$ are stopped in a LOW/HIGH state. When OMODE is LOW, the outputs are tri-stated. Set $\overline{PD}$ HIGH for normal operation.            |

| LOCK     | 0   | LVTTL                     | PLL lock indication signal. HIGH indicates lock. LOW indicates that the PLL is not locked and outputs may not be synchronized to the                                                                                                                                                                                                                                                                                                                                                                                 |

|          |     |                           | inputs. (For more information on application specific use of the LOCK pin, please see AN237.)                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OMODE    | I   | LVTTL <sup>(1)</sup>      | Output disable control. Determines the outputs' disable state. Used in conjunction with nsOE and PD. (See Output Enable/Disable and                                                                                                                                                                                                                                                                                                                                                                                  |

|          |     |                           | Powerdowntables.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VDDQ     |     | PWR                       | Power supply for output buffers. When using 2.5V LVTTL, VDDQ should be connected to VDD.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VDD      |     | PWR                       | Power supply for phase locked loop, lock output, inputs, and other internal circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                |

| GND      |     | PWR                       | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### NOTES:

- 1. Pins listed as LVTTL inputs will accept 2.5V signals under all conditions. If the output is operating at 1.8V or 1.5V, the LVTTL inputs will accept the 1.8V LVTTL signals as well.

- 2. Outputs are user selectable to drive 2.5V, 1.8V LVTTL, eHSTL, or HSTL interface levels when used with the appropriate VDDQ voltage.

- 3. 3-level inputs are static inputs and must be tied to VDD or GND or left floating. These inputs are not hot-insertable or over voltage tolerant.

## OUTPUT ENABLE/DISABLE

| nsOE | OMODE | Output               |

|------|-------|----------------------|

| L    | Χ     | Normal Operation     |

| Н    | L     | Tri-State            |

| Н    | Н     | Gated <sup>(1)</sup> |

#### NOTE:

1. PE determines the level at which the outputs stop. When PE is LOW/HIGH, the nQ is stopped in a HIGH/LOW state while the  $\overline{nQ}$  is stopped at a LOW/HIGH state.

## **POWERDOWN**

| PD | OMODE | Output               |

|----|-------|----------------------|

| Н  | Х     | Normal Operation     |

| L  | L     | Tri-State            |

| L  | Н     | Gated <sup>(1)</sup> |

## NOTE:

1. PE determines the level at which the outputs stop. When PE is LOW/HIGH, the nQ and QFB are stopped in a HIGH/LOW state, while the  $\overline{nQ}$  and  $\overline{QFB}$  are stopped in a LOW/HIGH state.

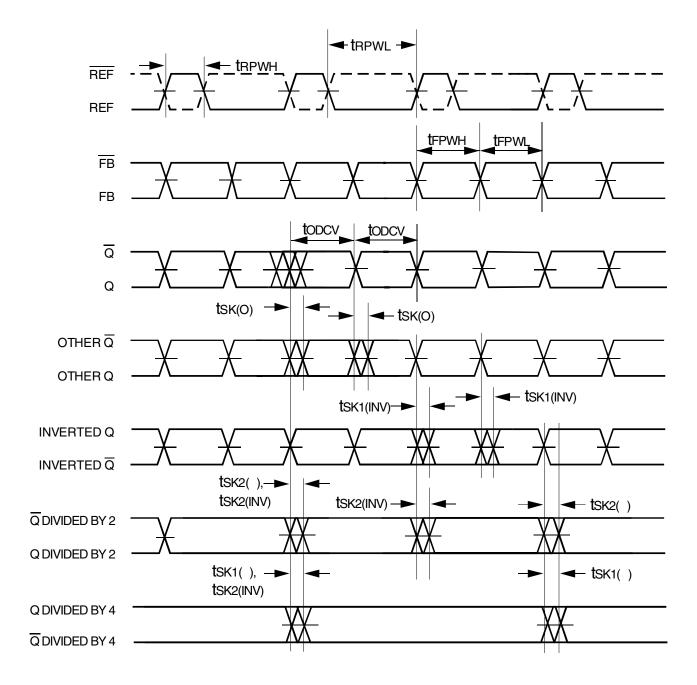

## **PROGRAMMABLE SKEW**

Output skew with respect to the REF[1:0] and REF[1:0]/VREF[1:0] input is adjustable to compensate for PCB trace delays, backplane propagation delays or to accommodate requirements for special timing relationships between clocked components. Skew is selectable as a multiple of a time unit (tu) which ranges from 250ps to 1.25ns (see Programmable Skew Range and Resolution Table). There are 18 skew/divide configurations available for each output pair. These configurations are chosen by the

nF[2:0]/FBF[2:0] control pins. In order to minimize the number of control pins, 3-level inputs (HIGH-MID-LOW) are used, they are intended for but not restricted to hard-wiring. Undriven 3-level inputs default to the MID level. The Control Summary Table shows how to select specific skew taps by using the nF[2:0]/FBF[2:0] control pins.

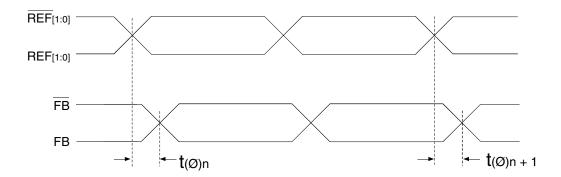

#### EXTERNAL DIFFERENTIAL FEEDBACK

By providing a dedicated external differential feedback, the IDT5T9110 gives users flexibility with regard to skew adjustment. The FB and  $\overline{\text{FB}}$ /VREF2 signals are compared with the input REF[1:0] and  $\overline{\text{REF}}$ [1:0]/VREF[1:0] signals at the phase detector in order to drive the VCO. Phase differences cause the VCO of the PLL to adjust upwards or downwards accordingly.

An internal loop filter moderates the response of the VCO to the phase detector. The loop filter transfer function has been chosen to provide minimal jitter (or frequency variation) while still providing accurate responses to input frequency changes.

#### PROGRAMMABI F SKFWRANGF AND RESOLUTION TABLE

|                                             | FS = LOW      | FS = HIGH     | Comments        |

|---------------------------------------------|---------------|---------------|-----------------|

| Timing Unit Calculation (tu)                | 1/(16 x Fnom) | 1/(16 x Fnom) |                 |

| VCO Frequency Range (FNOM) <sup>(1,2)</sup> | 50 to 125MHz  | 100 to 250MHz |                 |

| Skew Adjustment Range <sup>(3)</sup>        |               |               |                 |

| Max Adjustment:                             | ±8.75ns       | ±4.375ns      | ns              |

| Ι                                           | ±157.5°       | ±157.5°       | Phase Degrees   |

|                                             | ±43.75%       | ±43.75%       | % of Cycle Time |

| Example 1, Fnoм = 50MHz                     | tu = 1.25ns   | _             |                 |

| Example 2, FNOM = 75MHz                     | tu = 0.833ns  | _             |                 |

| Example 3, FNOM = 100MHz                    | tu = 0.625ns  | tu = 0.625ns  |                 |

| Example 4, FNOM = 150MHz                    | _             | tu = 0.417ns  |                 |

| Example 5, FNOM = 200MHz                    | _             | tu = 0.313ns  |                 |

| Example 6, FNOM = 250MHz                    |               | tu = 0.25ns   |                 |

- 1. The device may be operated outside recommended frequency ranges without damage, but functional operation is not guaranteed.

- 2. The level to be set on FS is determined by the nominal operating frequency of the VCO and Time Unit Generator. The VCO frequency always appears at nQ and nQ outputs when they are operated in their undivided modes. The frequency appearing at the REF[1:0] and REF[1:0]/VREF[1:0] and FB and FB/VREF2 inputs will be FNOM when the QFB and QFB are undivided and DS[1:0] = MM. The frequency of the REF[1:0] and REF[1:0]/VREF[1:0] and FB and FB/VREF2 inputs will be FNOM /2 or FNOM /4 when the part is configured for frequency multiplication by using a divided QFB and QFB and setting DS[1:0] = MM. Using the DS[1:0] inputs allows a different method for frequency multiplication (see Divide Selection Table).

- 3. Skew adjustment range assumes that a zero skew output is used for feedback. If a skewed QFB and QFB output is used for feedback, then adjustment range will be greater. For example if a 4tu skewed output is used for feedback, all other outputs will be skewed -4tu in addition to whatever skew value is programmed for those outputs. 'Max adjustment' range applies to all output pairs where ±7tu skew adjustment is possible and at the lowest FNOM value.

## **DIVIDE SELECTION TABLE**

| DS [1:0] | Divide-by-n | Permitted Output Divide-by-n connected to FB and FB/VREF2 <sup>(1)</sup> |

|----------|-------------|--------------------------------------------------------------------------|

| Ш        | 2           | 1, 2                                                                     |

| LM       | 3           | 1                                                                        |

| LH       | 4           | 1, 2                                                                     |

| ML       | 5           | 1, 2                                                                     |

| MM       | 1           | 1, 2, 4                                                                  |

| МН       | 6           | 1, 2                                                                     |

| HL       | 8           | 1                                                                        |

| НМ       | 10          | 1                                                                        |

| НН       | 12          | 1                                                                        |

#### NOTE:

## CONTROL SUMMARY TABLE FOR ALL OUTPUTS(1)

| nF2/FBF2 | nF1/FBF1 | nFo/FBFo | Output Skew |

|----------|----------|----------|-------------|

| L        | L        | L        | Divide by 2 |

| L        | L        | M        | +7tu        |

| L        | L        | Н        | +6tU        |

| L        | M        | L        | +5tu        |

| L        | M        | M        | +4tu        |

| L        | M        | Н        | +3tu        |

| L        | Н        | L        | +2tu        |

| L        | Н        | M        | +1tu        |

| L        | Н        | Н        | Zero Skew   |

| Н        | L        | L        | Inverted    |

| Н        | L        | M        | -1tu        |

| Н        | L        | Н        | -2tu        |

| Н        | M        | L        | -3tu        |

| Н        | M        | M        | -4tu        |

| Н        | M        | Н        | -5tu        |

| Н        | Н        | L        | -6tu        |

| Н        | Н        | M        | -7tu        |

| Н        | Н        | Н        | Divide by 4 |

<sup>1.</sup> Permissible output division ratios connected to FB and FB/VREF2. The frequencies of the REF[1:0] and REF[1:0]/VREF[1:0] inputs will be FNoM/N when the parts are configured for frequency multiplication by using an undivided output for FB and FB/VREF2 and setting DS[1:0] to N (N = 1-6, 8, 10, 12).

<sup>1.</sup> When PLL\_EN is HIGH, the PLL is disabled and the device is put into test mode. In test mode, 5F[2:0] must be set to MHL, the REF[1:0]/REF[1:0] input frequency must be set to 1MHz or less, and nF[2:0]/FBF[2:0] pins should be set to LHH.

## INPUT/OUTPUT SELECTION<sup>(1)</sup>

| TIVI OT/OUT OT SELEC | 311014    |

|----------------------|-----------|

| Input                | Output    |

| 2.5V LVTTL SE        | 2.5VLVTTL |

| 1.8V LVTTL SE        |           |

| 2.5V LVTTL DSE       |           |

| 1.8V LVTTL DSE       |           |

| LVEPECL DSE          |           |

| eHSTL DSE            |           |

| HSTL DSE             |           |

| 2.5V LVTTL DIF       |           |

| 1.8V LVTTL DIF       |           |

| LVEPECL DIF          |           |

| eHSTL DIF            |           |

| HSTL DIF             |           |

| 2.5V LVTTL SE        | 1.8VLVTTL |

| 1.8V LVTTL SE        |           |

| 2.5V LVTTL DSE       |           |

| 1.8V LVTTL DSE       |           |

| LVEPECL DSE          |           |

| eHSTL DSE            |           |

| HSTL DSE             |           |

| 2.5V LVTTL DIF       |           |

| 1.8V LVTTL DIF       |           |

| LVEPECL DIF          |           |

| eHSTL DIF            |           |

| HSTL DIF             | 7         |

| Input          | Output |

|----------------|--------|

| 2.5V LVTTL SE  | eHSTL  |

| 1.8V LVTTL SE  |        |

| 2.5V LVTTL DSE |        |

| 1.8V LVTTL DSE |        |

| LVEPECL DSE    |        |

| eHSTL DSE      |        |

| HSTL DSE       |        |

| 2.5V LVTTL DIF |        |

| 1.8V LVTTL DIF |        |

| LVEPECL DIF    |        |

| eHSTL DIF      |        |

| HSTL DIF       |        |

| 2.5V LVTTL SE  | HSTL   |

| 1.8V LVTTL SE  |        |

| 2.5V LVTTL DSE |        |

| 1.8V LVTTL DSE |        |

| LVEPECL DSE    |        |

| eHSTL DSE      |        |

| HSTL DSE       |        |

| 2.5V LVTTL DIF |        |

| 1.8V LVTTL DIF |        |

| LVEPECL DIF    |        |

| eHSTL DIF      |        |

| HSTL DIF       |        |

#### NOTE:

## DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

| Symbol     | Parameter                              |                     | Min.                                          | Max         | Unit        |    |

|------------|----------------------------------------|---------------------|-----------------------------------------------|-------------|-------------|----|

| Vihh       | Input HIGH Voltage Level(1)            | 3-Level Inputs Only |                                               | VDD - 0.4   | _           | V  |

| VIMM       | Input MID Voltage Level(1)             | 3-Level Inputs Only |                                               | VDD/2 - 0.2 | VDD/2 + 0.2 | V  |

| VILL       | Input LOW Voltage Level <sup>(1)</sup> | 3-Level Inputs Only |                                               | _           | 0.4         | V  |

|            |                                        | VIN = VDD           | HIGH Level                                    | _           | 200         |    |

| <b>I</b> 3 | 3-Level Input DC Current               | $V_{IN} = V_{DD}/2$ | MID Level                                     | -50         | +50         | μΑ |

|            | (RxS, TxS, nF[2:0], FBF[2:0], DS[1:0]) | VIN = GND           | LOW Level                                     | -200        | _           |    |

| lpu        | Input Pull-Up Current (PE)             | VDD = Max., VIN = G | V <sub>DD</sub> = Max., V <sub>IN</sub> = GND |             | _           | μΑ |

<sup>1.</sup> The INPUT/OUTPUT SELECTION Table describes the total possible combinations of input and output interfaces. Single-Ended (SE) inputs in a single-ended mode require the REF[1:0]/VREF[1:0] and FB/VREF2 pins to be left floating. Differential Single-Ended (DSE) is for single-ended operation in differential mode, requiring VREF[1:0] and VREF2. Differential (DIF) inputs are used only in differential mode.

<sup>1.</sup> These inputs are normally wired to Vpb, GND, or left floating. Internal termination resistors bias unconnected inputs to Vpb/2. If these inputs are switched dynamically after powerup, the function and timing of the outputs may be glitched, and the PLL may require additional tLock time before all datasheet limits are achieved.

## DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE FOR HSTL(1)

| Symbol       | Parameter                                     | Test Conditions   |                       | Min.         | Typ. <sup>(7)</sup> | Max          | Unit |

|--------------|-----------------------------------------------|-------------------|-----------------------|--------------|---------------------|--------------|------|

| Input Charac | cteristics                                    | -                 |                       |              |                     | -            |      |

| Іін          | Input HIGH Current                            | VDD = 2.7V        | Vi = Vddq/GND         | _            | _                   | ±5           | μΑ   |

| lıL          | Input LOW Current                             | VDD = 2.7V        | $V_{I} = GND/V_{DDQ}$ | _            | _                   | ±5           |      |

| Vik          | Clamp Diode Voltage                           | VDD = 2.3V, IIN = | -18mA                 | _            | - 0.7               | - 1.2        | V    |

| Vin          | DC Input Voltage                              |                   |                       | - 0.3        |                     | +3.6         | V    |

| VDIF         | DC Differential Voltage <sup>(2,8)</sup>      |                   |                       | 0.2          |                     | _            | V    |

| Vсм          | DC Common Mode Input Voltage <sup>(3,8)</sup> |                   |                       | 680          | 750                 | 900          | mV   |

| ViH          | DC Input HIGH <sup>(4,5,8)</sup>              |                   |                       | VREF + 100   |                     | _            | mV   |

| VIL          | DC Input LOW <sup>(4,6,8)</sup>               |                   |                       | _            |                     | Vref - 100   | mV   |

| Vref         | Single-Ended Reference Voltage(4,8)           |                   |                       | _            | 750                 | _            | mV   |

| Output Char  | acteristics                                   |                   |                       |              |                     |              |      |

| Vон          | Output HIGH Voltage                           | Іон = -8mA        |                       | VDDQ - 0.4   |                     | _            | V    |

|              |                                               | Іон = -100μА      |                       | VDDQ - 0.1   |                     | _            |      |

| Vol          | Output LOW Voltage                            | IoL = 8mA         |                       | _            |                     | 0.4          | V    |

|              |                                               | IoL = 100μA       |                       | _            |                     | 0.1          |      |

| Vox          | FB/FB Output Crossing Point                   | _                 | _                     | VDDQ/2 - 150 | VDDQ/2              | VDDQ/2 + 150 | mV   |

#### NOTES:

- 1. See RECOMMENDED OPERATING RANGE table.

- 2. VDIF specifies the minimum input differential voltage (VTR VCP) required for switching where VTR is the "true" input level and VCP is the "complement" input level. Differential mode only. The DC differential voltage must be maintained to guarantee retaining the existing HIGH or LOW input. The AC differential voltage must be achieved to guarantee switching to a new state.

- 3. Vcm specifies the maximum allowable range of (VTR + VCP) /2. Differential mode only.

- 4. For single-ended operation, in differential mode, REF[1:0]/VREF[1:0] is tied to the DC voltage VREF[1:0].

- 5. Voltage required to maintain a logic HIGH, single-ended operation in differential mode.

- ${\it 6. \ Voltage \ required \ to \ maintain \ a \ logic \ LOW, \ single-ended \ operation \ in \ differential \ mode.}$

- 7. Typical values are at VDD = 2.5V, VDDQ = 1.5V, +25°C ambient.

- 8. The reference clock input is capable of HSTL, eHSTL, LVEPECL, 1.8V or 2.5V LVTTL operation independent of the device output. (See Input/Output Selection table.)

## POWER SUPPLY CHARACTERISTICS FOR HSTL OUTPUTS(1)

| Symbol | Parameter                                     | Test Conditions <sup>(2)</sup>                                                         | Тур. | Max | Unit   |

|--------|-----------------------------------------------|----------------------------------------------------------------------------------------|------|-----|--------|

| IDDQ   | Quiescent Vdd Power Supply Current(3)         | VDDQ = Max., REF = LOW, PD = HIGH, nSOE = LOW,                                         | 100  | 150 | mA     |

|        |                                               | $\overline{\text{PLL\_EN}} = \text{HIGH, DS}[1:0] = \text{MM, nF}[2:0] = \text{LHH,}$  |      |     |        |

|        |                                               | FBF[2:0] = LHH, Outputs enabled, All outputs unloaded                                  |      |     |        |

| Iddaa  | Quiescent VDDQ Power Supply Current(3)        | VDDQ = Max., REF = LOW, PD = HIGH, nSOE = LOW,                                         | 0.75 | 50  | μΑ     |

|        |                                               | $\overline{\text{PLL}_{EN}} = \text{HIGH}, DS[1:0] = MM, nF[2:0] = LHH,$               |      |     |        |

|        |                                               | FBF[2:0] = LHH, Outputs enabled, All outputs unloaded                                  |      |     |        |

| Iddpd  | Power Down Current                            | $V_{DD} = Max., \overline{PD} = LOW, \overline{nSOE} = LOW, \overline{PLL\_EN} = HIGH$ | 1.7  | 5   | mA     |

| IDDD   | Dynamic Vod Power Supply                      | VDD = Max., VDDQ = Max., CL = 0pF                                                      | 19   | 30  | μA/MHz |

|        | Current per Output                            |                                                                                        |      |     |        |

| IDDDQ  | Dynamic VDDQ Power Supply                     | VDD = Max., VDDQ = Max., CL = 0pF                                                      | 18   | 30  | μA/MHz |

|        | Current per Output                            |                                                                                        |      |     |        |

| Ітот   | Total Power Vdd Supply Current <sup>(4)</sup> | VDDQ = 1.5V, Fvco = 100MHz, CL = 15pF                                                  | 115  | 170 | mA     |

|        |                                               | VDDQ = 1.5V, Fvco = 250MHz, CL = 15pF                                                  | 150  | 225 |        |

| Ітото  | Total Power Vdda Supply Current(4)            | VDDQ = 1.5V, Fvco = 100MHz, CL = 15pF                                                  | 45   | 70  | mA     |

|        |                                               | VDDQ = 1.5V, Fvco = 250MHz, CL = 15pF                                                  | 100  | 150 | 1      |

- 1. These power consumption characteristics are for all the valid input interfaces and cover the worst case input and output interface combinations.

- 2. The termination resistors are excluded from these measurements.

- 3. If the differential input interface is used, the true input is held LOW and the complementary input is held HIGH.

- 4. FS = HIGH.

## DIFFERENTIAL INPUT AC TEST CONDITIONS FOR HSTL

| Symbol           | Parameter                                               | Value          | Units |

|------------------|---------------------------------------------------------|----------------|-------|

| VDIF             | Input Signal Swing <sup>(1)</sup>                       | 1              | V     |

| Vx               | Differential Input Signal Crossing Point <sup>(2)</sup> | 750            | mV    |

| V <sub>THI</sub> | Input Timing Measurement Reference Level <sup>(3)</sup> | Crossing Point | V     |

| tr, tr           | Input Signal Edge Rate <sup>(4)</sup>                   | 1              | V/ns  |

#### NOTES:

- 1. The 1V peak-to-peak input pulse level is specified to allow consistent, repeatable results in an automatic test equipment (ATE) environment. This device meets the VDIF (AC) specification under actual use conditions.

- 2. A 750mV crossing point level is specified to allow consistent, repeatable results in an automatic test equipment (ATE) environment. This device meets the Vx specification under actual use conditions.

- 3. In all cases, input waveform timing is marked at the differential cross-point of the input signals.

- 4. The input signal edge rate of 1V/ns or greater is to be maintained in the 20% to 80% range of the input waveform.

## DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE FOR eHSTL(1)

| Symbol      | Parameter                                       | Test Conditions        |               | Min.         | Typ. <sup>(7)</sup> | Max          | Unit |  |  |

|-------------|-------------------------------------------------|------------------------|---------------|--------------|---------------------|--------------|------|--|--|

| Input Chara | Input Characteristics                           |                        |               |              |                     |              |      |  |  |

| Іін         | Input HIGH Current                              | V <sub>DD</sub> = 2.7V | VI = VDDQ/GND | _            | _                   | ±5           | μΑ   |  |  |

| lıL         | Input LOW Current                               | V <sub>DD</sub> = 2.7V | VI = GND/VDDQ | _            | _                   | ±5           |      |  |  |

| Vik         | Clamp Diode Voltage                             | VDD = 2.3V, IIN =      | -18mA         | _            | - 0.7               | - 1.2        | V    |  |  |

| Vin         | DC Input Voltage                                |                        |               | - 0.3        |                     | +3.6         | V    |  |  |

| Vdif        | DC Differential Voltage <sup>(2,8)</sup>        |                        |               | 0.2          |                     | _            | V    |  |  |

| Vсм         | DC Common Mode Input Voltage <sup>(3,8)</sup>   |                        |               | 800          | 900                 | 1000         | mV   |  |  |

| ViH         | DC Input HIGH(4,5,8)                            |                        |               | Vref + 100   |                     | _            | mV   |  |  |

| VIL         | DC Input LOW <sup>(4,6,8)</sup>                 |                        |               | _            |                     | VREF - 100   | mV   |  |  |

| Vref        | Single-Ended Reference Voltage <sup>(4,8)</sup> |                        |               | _            | 900                 | _            | mV   |  |  |

| Output Char | racteristics                                    | •                      |               |              |                     |              |      |  |  |

| Vон         | Output HIGH Voltage                             | Іон = -8mA             |               | VDDQ - 0.4   |                     | _            | V    |  |  |

|             |                                                 | Іон = -100μА           |               | VDDQ - 0.1   |                     | _            | V    |  |  |

| Vol         | Output LOW Voltage                              | IoL = 8mA              |               | _            |                     | 0.4          | V    |  |  |

|             |                                                 | IoL = 100μA            |               | _            |                     | 0.1          | V    |  |  |

| Vox         | FB/FB Output Crossing Point                     |                        |               | VDDQ/2 - 150 | VDDQ/2              | VDDQ/2 + 150 | mV   |  |  |

- 1. See RECOMMENDED OPERATING RANGE table.

- 2. Voir specifies the minimum input differential voltage (VTR VCP) required for switching where VTR is the "true" input level and VCP is the "complement" input level. Differential mode only. The DC differential voltage must be maintained to guarantee retaining the existing HIGH or LOW input. The AC differential voltage must be achieved to guarantee switching to a new state.

- 3. Vcm specifies the maximum allowable range of (VTR + VcP) /2. Differential mode only.

- 4. For single-ended operation, in a differential mode, REF[1:0]/VREF[1:0] is tied to the DC voltage VREF[1:0].

- 5. Voltage required to maintain a logic HIGH, single-ended operation in differential mode.

- 6. Voltage required to maintain a logic LOW, single-ended operation in differential mode.

- 7. Typical values are at VDD = 2.5V, VDDQ = 1.8V, +25°C ambient.

- 8. The reference clock input is capable of HSTL, eHSTL, LVEPECL, 1.8V or 2.5V LVTTL operation independent of the device output. (See Input/Output Selection table.)

### 2.5V PROGRAMMABLE SKEW PLL DIFFERENTIAL CLOCK DRIVER TERACLOCK

## POWER SUPPLY CHARACTERISTICS FOR eHSTL OUTPUTS(1)

| Symbol | Parameter                              | Test Conditions <sup>(2)</sup>                                                               | Тур. | Max | Unit   |

|--------|----------------------------------------|----------------------------------------------------------------------------------------------|------|-----|--------|

| IDDQ   | Quiescent Vdd Power Supply Current(3)  | VDDQ = Max., REF = LOW, PD = HIGH, nSOE = LOW,                                               | 100  | 150 | mA     |

|        |                                        | $\overline{\text{PLL}_{EN}} = \text{HIGH}, DS[1:0] = MM, nF[2:0] = LHH,$                     |      |     |        |

|        |                                        | FBF[2:0] = LHH, Outputs enabled, All outputs unloaded                                        |      |     |        |

| Iddag  | Quiescent VDDQ Power Supply Current(3) | VDDQ = Max., REF = LOW, PD = HIGH, nSOE = LOW,                                               | 1.8  | 50  | μΑ     |

|        |                                        | $\overline{\text{PLL}}_{EN} = \text{HIGH, DS}_{[1:0]} = \text{MM, nF}_{[2:0]} = \text{LHH,}$ |      |     |        |

|        |                                        | FBF[2:0] = LHH, Outputs enabled, All outputs unloaded                                        |      |     |        |

| Iddpd  | Power Down Current                     | $V_{DD} = Max., \overline{PD} = LOW, \overline{nSOE} = LOW, \overline{PLL\_EN} = HIGH$       | 1.7  | 5   | mA     |

| Iddd   | Dynamic Vod Power Supply               | VDD = Max., VDDQ = Max., CL = OpF                                                            | 19   | 30  | μA/MHz |

|        | Current per Output                     |                                                                                              |      |     |        |

| IDDDQ  | Dynamic VDDQ Power Supply              | VDD = Max., VDDQ = Max., CL = 0pF                                                            | 20   | 30  | μA/MHz |

|        | Current per Output                     |                                                                                              |      |     |        |

| Ітот   | Total Power Vdd Supply Current(4)      | VDDQ = 1.8V, Fvco = 100MHz, CL = 15pF                                                        | 115  | 170 | mA     |

|        |                                        | VDDQ = 1.8V, Fvco = 250MHz, CL = 15pF                                                        | 150  | 225 |        |

| Ітото  | Total Power VDDQ Supply Current(4)     | VDDQ = 1.8V, Fvco = 100MHz, CL = 15pF                                                        | 55   | 80  | mA     |

|        |                                        | VDDQ = 1.8V, Fvco = 250MHz, CL = 15pF                                                        | 140  | 210 |        |

#### NOTES:

- 1. These power consumption characteristics are for all the valid input interfaces and cover the worst case input and output interface combinations.

- 2. The termination resistors are excluded from these measurements.

- 3. If the differential input interface is used, the true input is held LOW and the complementary input is held HIGH.

- 4. FS = HIGH.

## DIFFERENTIAL INPUT AC TEST CONDITIONS FOR eHSTL

| Symbol | Parameter                                               | Value          | Units |

|--------|---------------------------------------------------------|----------------|-------|

| VDIF   | Input Signal Swing <sup>(1)</sup>                       | 1              | V     |

| Vx     | Differential Input Signal Crossing Point <sup>(2)</sup> | 900            | mV    |

| Vтні   | Input Timing Measurement Reference Level <sup>(3)</sup> | Crossing Point | V     |

| tr, tr | Input Signal Edge Rate <sup>(4)</sup>                   | 1              | V/ns  |

- 1. The 1V peak-to-peak input pulse level is specified to allow consistent, repeatable results in an automatic test equipment (ATE) environment. This device meets the VDIF (AC) specification under actual use conditions.

- 2. A 900mV crossing point level is specified to allow consistent, repeatable results in an automatic test equipment (ATE) environment. This device meets the Vx specification under actual use conditions.

- 3. In all cases, input waveform timing is marked at the differential cross-point of the input signals.

- 4. The input signal edge rate of 1V/ns or greater is to be maintained in the 20% to 80% range of the input waveform.

# DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE FOR LVEPECL<sup>(1)</sup>

| Symbol                | Parameter                           | Test Conditions                                 |                       | Min.  | Typ. <sup>(2)</sup> | Max   | Unit |  |

|-----------------------|-------------------------------------|-------------------------------------------------|-----------------------|-------|---------------------|-------|------|--|

| Input Characteristics |                                     |                                                 |                       |       |                     |       |      |  |

| Іін                   | Input HIGH Current                  | VDD = 2.7V                                      | $V_{I} = V_{DDQ}/GND$ | _     | ı                   | ±5    | μΑ   |  |

| lιL                   | Input LOW Current                   | $V_{DD} = 2.7V$                                 | $V_I = GND/V_{DDQ}$   | _     | ı                   | ±5    |      |  |

| Vik                   | Clamp Diode Voltage                 | V <sub>DD</sub> = 2.3V, I <sub>IN</sub> = -18mA |                       | _     | - 0.7               | - 1.2 | V    |  |

| Vin                   | DC Input Voltage                    |                                                 |                       | - 0.3 | _                   | 3.6   | V    |  |

| Vсм                   | DC Common Mode Input Voltage(3,5)   |                                                 |                       | 915   | 1082                | 1248  | mV   |  |

| Vref                  | Single-Ended Reference Voltage(4,5) |                                                 |                       | _     | 1082                | _     | mV   |  |

| ViH                   | DC Input HIGH                       |                                                 | ·                     | 1275  | _                   | 1620  | mV   |  |

| VIL                   | DC Input LOW                        |                                                 | ·                     | 555   | _                   | 875   | mV   |  |

#### NOTES:

- 1. See RECOMMENDED OPERATING RANGE table.

- 2. Typical values are at V<sub>DD</sub> = 2.5V, +25°C ambient.

- 3. Vcm specifies the maximum allowable range of (VTR + VCP) /2. Differential mode only.

- 4. For single-ended operation while in differential mode, REF[1:0]/VREF[1:0] is tied to the DC voltage VREF[1:0].

- 5. The reference clock input is capable of HSTL, eHSTL, LVEPECL, 1.8V or 2.5V LVTTL operation independent of the device output. (See Input/Output Selection table.)

## DIFFERENTIAL INPUT AC TEST CONDITIONS FOR LVEPECL

| Symbol | Parameter                                               | Value          | Units |

|--------|---------------------------------------------------------|----------------|-------|

| VDIF   | Input Signal Swing <sup>(1)</sup>                       | 732            | mV    |

| Vx     | Differential Input Signal Crossing Point <sup>(2)</sup> | 1082           | mV    |

| Vтні   | Input Timing Measurement Reference Level <sup>(3)</sup> | Crossing Point | V     |

| tr, tr | Input Signal Edge Rate <sup>(4)</sup>                   | 1              | V/ns  |

- 1. The 732mV peak-to-peak input pulse level is specified to allow consistent, repeatable results in an automatic test equipment (ATE) environment. This device meets the VDIF (AC) specification under actual use conditions.

- 2. A 1082mV crossing point level is specified to allow consistent, repeatable results in an automatic test equipment (ATE) environment. This device meets the Vx specification under actual use conditions.

- 3. In all cases, input waveform timing is marked at the differential cross-point of the input signals.

- 4. The input signal edge rate of 1V/ns or greater is to be maintained in the 20% to 80% range of the input waveform.

# DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE FOR 2.5V LVTTL<sup>(1)</sup>

| Symbol       | Parameter                                       | Test Conditions        |                       | Min.       | Typ. <sup>(8)</sup> | Max        | Unit |

|--------------|-------------------------------------------------|------------------------|-----------------------|------------|---------------------|------------|------|

| Input Chara  | cteristics                                      |                        |                       |            |                     |            |      |

| Іін          | Input HIGH Current                              | VDD = 2.7V             | $V_{I} = V_{DDQ}/GND$ | _          | _                   | ±5         | μА   |

| lı∟          | Input LOW Current                               | V <sub>DD</sub> = 2.7V | $V_{I} = GND/V_{DDQ}$ | _          | _                   | ±5         |      |

| Vik          | Clamp Diode Voltage                             | VDD = 2.3V, IIN =      | -18mA                 |            | - 0.7               | - 1.2      | V    |

| Vin          | DC Input Voltage                                |                        |                       | - 0.3      |                     | +3.6       | V    |

| Single-End   | ed Inputs <sup>(2)</sup>                        | •                      |                       |            |                     |            |      |

| ViH          | DC Input HIGH                                   |                        |                       | 1.7        |                     | _          | V    |

| VIL          | DC Input LOW                                    |                        |                       |            |                     | 0.7        | V    |

| Differential | Inputs                                          | -                      |                       |            |                     | -          |      |

| Vdif         | DC Differential Voltage <sup>(3,9)</sup>        |                        |                       | 0.2        |                     | _          | V    |

| Vсм          | DC Common Mode Input Voltage <sup>(4,9)</sup>   |                        |                       | 1150       | 1250                | 1350       | mV   |

| ViH          | DC Input HIGH <sup>(5,6,9)</sup>                |                        |                       | VREF + 100 |                     | _          | mV   |

| VIL          | DC Input LOW <sup>(5,7,9)</sup>                 |                        |                       |            |                     | VREF - 100 | mV   |

| Vref         | Single-Ended Reference Voltage <sup>(5,9)</sup> |                        |                       | _          | 1250                | _          | mV   |

| Output Cha   | racteristics                                    |                        |                       |            |                     |            |      |

| Vон          | Output HIGH Voltage                             | Iон = -12mA            |                       | VDDQ - 0.4 |                     | _          | V    |

|              |                                                 | Іон = -100μА           |                       | VDDQ - 0.1 |                     | _          | V    |

| Vol          | Output LOW Voltage                              | IoL = 12mA             |                       | _          |                     | 0.4        | V    |

|              |                                                 | IoL = 100μA            | _                     | [          | ·                   | 0.1        | V    |

- 1. See RECOMMENDED OPERATING RANGE table.

- 2. For 2.5V LVTTL single-ended operation, the RxS pin is tied HIGH and REF[1:0]/VREF[1:0] is left floating. If TxS is HIGH, FB/VREF2 should be left floating.

- 3. VDIF specifies the minimum input differential voltage (VTR VCP) required for switching where VTR is the "true" input level and VCP is the "complement" input level. Differential mode only. The DC differential voltage must be maintained to guarantee retaining the existing HIGH or LOW input. The AC differential voltage must be achieved to guarantee switching to a new state.

- 4. Vcm specifies the maximum allowable range of (VTR + VcP) /2. Differential mode only.

- 5. For single-ended operation, in differential mode, REF[1:0]/VREF[1:0] is tied to the DC voltage VREF[1:0].

- 6. Voltage required to maintain a logic HIGH, single-ended operation in differential mode.

- 7. Voltage required to maintain a logic LOW, single-ended operation in differential mode.

- 8. Typical values are at VDD = 2.5V, VDDQ = VDD, +25°C ambient.

- 9. The reference clock input is capable of HSTL, eHSTL, LVEPECL, 1.8V or 2.5V LVTTL operation independent of the device output. (See Input/Output Selection table.)

## POWER SUPPLY CHARACTERISTICS FOR 2.5V LVTTL OUTPUTS(1)

| Symbol | Parameter                                     | Test Conditions <sup>(2)</sup>                                                         | Тур. | Max | Unit   |

|--------|-----------------------------------------------|----------------------------------------------------------------------------------------|------|-----|--------|

| DDDQ   | Quiescent VDD Power Supply Current(3)         | $V_{DDQ} = Max., REF = LOW, \overline{PD} = HIGH, \overline{nSOE} = LOW,$              | 100  | 150 | mA     |

|        |                                               | $\overline{\text{PLL}_{EN}} = \text{HIGH}, DS[1:0] = MM, nF[2:0] = LHH,$               |      |     |        |

|        |                                               | FBF[2:0] = LHH, Outputs enabled, All outputs unloaded                                  |      |     |        |

| Iddqq  | Quiescent VDDQ Power Supply Current(3)        | $V_{DDQ} = Max., REF = LOW, \overline{PD} = HIGH, \overline{nSOE} = LOW,$              | 10   | 50  | μА     |

|        |                                               | $\overline{\text{PLL}_{EN}} = \text{HIGH}, DS[1:0] = MM, nF[2:0] = LHH,$               |      |     |        |

|        |                                               | FBF[2:0] = LHH, Outputs enabled, All outputs unloaded                                  |      |     |        |

| Iddpd  | Power Down Current                            | $V_{DD} = Max., \overline{PD} = LOW, \overline{nSOE} = LOW, \overline{PLL\_EN} = HIGH$ | 1.7  | 5   | mA     |

| Iddd   | Dynamic Vod Power Supply                      | VDD = Max., VDDQ = Max., CL = 0pF                                                      | 21   | 30  | μA/MHz |

|        | Current per Output                            |                                                                                        |      |     |        |

| Idddq  | Dynamic VDDQ Power Supply                     | VDD = Max., VDDQ = Max., CL = 0pF                                                      | 33   | 40  | μA/MHz |

|        | Current per Output                            |                                                                                        |      |     |        |

| Ітот   | Total Power Vdd Supply Current <sup>(4)</sup> | VDDQ = 2.5V., FVCO = 100MHz, CL = 15pF                                                 | 115  | 170 | mA     |

|        |                                               | VDDQ = 2.5V., FVCO = 250MHz, CL = 15pF                                                 | 155  | 230 |        |

| Ιτοτο  | Total Power VDDQ Supply Current(4)            | VDDQ = 2.5V., Fvco = 100MHz, CL = 15pF                                                 | 80   | 120 | mA     |

|        |                                               | VDDQ = 2.5V., FVCO = 250MHz, CL = 15pF                                                 | 235  | 350 | ]      |

|        |                                               |                                                                                        |      |     |        |

#### NOTES:

- 1. These power consumption characteristics are for all the valid input interfaces and cover the worst case input and output interface combinations.

- 2. The termination resistors are excluded from these measurements.

- 3. If the differential input interface is used, the true input is held LOW and the complementary input is held HIGH.

- 4. FS = HIGH.

## DIFFERENTIAL INPUT AC TEST CONDITIONS FOR 2.5V LVTTL

| Symbol | Parameter                                               | Value              | Units |

|--------|---------------------------------------------------------|--------------------|-------|

| VDIF   | Input Signal Swing <sup>(1)</sup>                       | Vdd                | V     |

| Vx     | Differential Input Signal Crossing Point <sup>(2)</sup> | V <sub>DD</sub> /2 | V     |

| Vтні   | Input Timing Measurement Reference Level <sup>(3)</sup> | Crossing Point     | V     |

| tr, tr | Input Signal Edge Rate <sup>(4)</sup>                   | 2.5                | V/ns  |

#### NOTES:

- 1. A nominal 2.5V peak-to-peak input pulse level is specified to allow consistent, repeatable results in an automatic test equipment (ATE) environment. This device meets the VDIF (AC) specification under actual use conditions.

- 2. A nominal 1.25V crossing point level is specified to allow consistent, repeatable results in an automatic test equipment (ATE) environment. This device meets the Vx specification under actual use conditions.

- 3. In all cases, input waveform timing is marked at the differential cross-point of the input signals.

- 4. The input signal edge rate of 2.5V/ns or greater is to be maintained in the 20% to 80% range of the input waveform.

## SINGLE-ENDED INPUT AC TEST CONDITIONS FOR 2.5V LVTTL

| Symbol           | Parameter                                               | Value              | Units |

|------------------|---------------------------------------------------------|--------------------|-------|

| VIH              | Input HIGH Voltage                                      | Vdd                | V     |

| VIL              | Input LOW Voltage                                       | 0                  | V     |

| V <sub>THI</sub> | Input Timing Measurement Reference Level <sup>(1)</sup> | V <sub>DD</sub> /2 | V     |

| tr, tr           | Input Signal Edge Rate <sup>(2)</sup>                   | 2                  | V/ns  |

- 1. A nominal 1.25V timing measurement reference level is specified to allow constant, repeatable results in an automatic test equipment (ATE) environment.

- 2. The input signal edge rate of 2V/ns or greater is to be maintained in the 10% to 90% range of the input waveform.

## DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE FOR 1.8V

| Symbol      | Parameter                                       | Test Co                | onditions             | Min.       | Typ. <sup>(8)</sup> | Max        | Unit |

|-------------|-------------------------------------------------|------------------------|-----------------------|------------|---------------------|------------|------|

| Input Chara | acteristics                                     |                        |                       |            |                     |            |      |

| Іін         | Input HIGH Current                              | V <sub>DD</sub> = 2.7V | $V_{I} = V_{DDQ}/GND$ | _          | _                   | ±5         | μΑ   |

| lıL         | Input LOW Current                               | V <sub>DD</sub> = 2.7V | VI = GND/VDDQ         | _          | _                   | ±5         |      |

| Vik         | Clamp Diode Voltage                             | VDD = 2.3V, IIN =      | -18mA                 | _          | - 0.7               | - 1.2      | V    |

| Vin         | DC Input Voltage                                |                        |                       | - 0.3      |                     | VDDQ + 0.3 | V    |

| Single-End  | led Inputs <sup>(2)</sup>                       | •                      |                       |            |                     |            |      |

| ViH         | DC Input HIGH                                   |                        |                       | 1.073(10)  |                     | _          | V    |

| VIL         | DC Input LOW                                    |                        |                       | _          |                     | 0.683(11)  | V    |

| Differentia | Inputs                                          |                        |                       |            |                     |            |      |

| VDIF        | DC Differential Voltage <sup>(3,9)</sup>        |                        |                       | 0.2        |                     | _          | V    |

| Vсм         | DC Common Mode Input Voltage <sup>(4,9)</sup>   |                        |                       | 825        | 900                 | 975        | mV   |

| ViH         | DC Input HIGH(5,6,9)                            |                        |                       | VREF + 100 |                     | _          | mV   |

| VIL         | DC Input LOW <sup>(5,7,9)</sup>                 |                        |                       | _          |                     | VREF - 100 | mV   |

| Vref        | Single-Ended Reference Voltage <sup>(5,9)</sup> |                        |                       | _          | 900                 | _          | mV   |

| Output Cha  | racteristics                                    | -                      |                       | -          |                     | -          |      |

| Vон         | Output HIGH Voltage                             | Іон = -6mA             |                       | VDDQ - 0.4 |                     |            | V    |

|             |                                                 | Іон = -100μА           |                       | VDDQ - 0.1 |                     | _          | V    |

| Vol         | Output LOW Voltage                              | IoL = 6mA              |                       |            |                     | 0.4        | V    |

|             |                                                 | IoL = 100μA            |                       | _          |                     | 0.1        | V    |

- 1. See RECOMMENDED OPERATING RANGE table.

- 2. For 1.8V LVTTL single-ended operation, the RxS pin is MID and REF[1:0]/VREF[1:0] is left floating. If TxS is MID, FB/VREF2 should be left floating.

- 3. VDIF specifies the minimum input differential voltage (VTR VCP) required for switching where VTR is the "true" input level and VCP is the "complement" input level. Differential mode only. The DC differential voltage must be maintained to guarantee retaining the existing HIGH or LOW input. The AC differential voltage must be achieved to guarantee switching to a new state.

- 4. Vcm specifies the maximum allowable range of (VTR + Vcp) /2. Differential mode only.

- 5. For single-ended operation in differential mode, REF[1:0]/VREF[1:0] is tied to the DC voltage VREF[1:0]. The input is guaranteed to toggle within ±200mV of VREF[1:0] when VREF[1:0] is constrained within ±600mV and VDDI-600mV, where VDDI is the nominal 1.8V power supply of the device driving the REF[1:0] input. To guarantee switching in voltage range specified in the JEDEC 1.8V LVTTL interface specification, VREF[1:0] must be maintained at 900mV with appropriate tolerances.

- 6. Voltage required to maintain a logic HIGH, single-ended operation in differential mode.

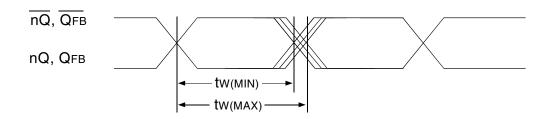

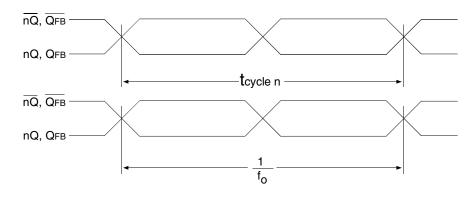

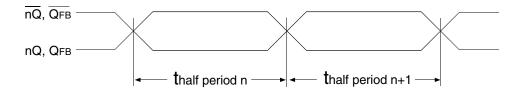

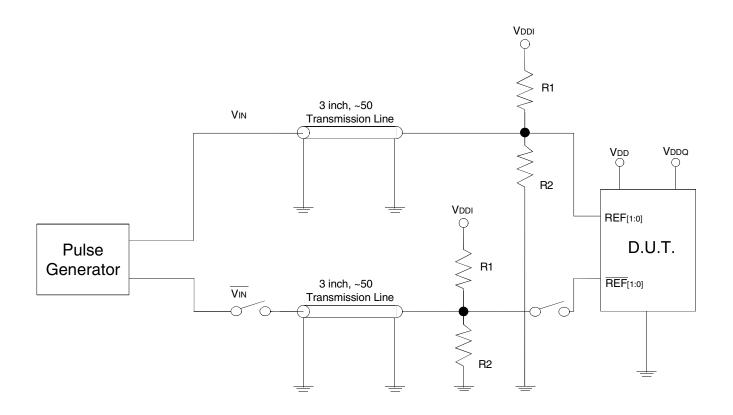

- 7. Voltage required to maintain a logic LOW, single-ended operation in differential mode.