# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# M16C/6N Group (M16C/6NK, M16C/6NM)

Hardware Manual

RENESAS MCU M16C FAMILY / M16C/60 SERIES

All information contained in this material, including products and product specifications at the time of publication of this material, is subject to change by Renesas Electronics Corp. without notice.

Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website

# Keep safety first in your circuit designs!

Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

### Notes regarding these materials -

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

- Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/ or the country of destination is prohibited.

- Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

#### General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

#### 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

— The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

#### 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

- In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

- 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

— The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

#### 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

— When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

#### 5. Differences between Products

Before changing from one product to another, i.e. to one with a different type number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different type numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different type numbers, implement a system-evaluation test for each of the products.

# How to Use This Manual

#### 1. Purpose and Target Readers

This manual is designed to provide the user with an understanding of the hardware functions and electrical characteristics of the MCU. It is intended for users designing application systems incorporating the MCU. A basic knowledge of electric circuits, logical circuits, and MCUs is necessary in order to use this manual. The manual comprises an overview of the product; descriptions of the CPU, system control functions, peripheral functions, and electrical characteristics; and usage notes.

Particular attention should be paid to the precautionary notes when using the manual. These notes occur within the body of the text, at the end of each section, and in the Usage Notes section.

The revision history summarizes the locations of revisions and additions. It does not list all revisions. Refer to the text of the manual for details.

The following documents apply to the M16C/6N Group (M16C/6NK, M16C/6NM). Make sure to refer to the latest versions of these documents. The newest versions of the documents listed may be obtained from the Renesas Technology Web site.

| Document Type    | Description                                      | Document Title       | Document No.  |

|------------------|--------------------------------------------------|----------------------|---------------|

| Datasheet        | Hardware overview and                            | M16C/6N Group        | REJ03B0058    |

|                  | electrical characteristics                       | (M16C/6NK, M16C/6NM) |               |

|                  |                                                  | Datasheet            |               |

| Hardware manual  | Hardware specifications (pin assignments,        | M16C/6N Group        | This hardware |

|                  | memory maps, peripheral function specifications, | (M16C/6NK. M16C/6NM) | manual        |

|                  | electrical characteristics, timing charts) and   | Hardware Manual      | (REJ09B0124)  |

|                  | operation description                            |                      |               |

|                  | Note: Refer to the application notes for details |                      |               |

|                  | on using peripheral functions.                   |                      |               |

| Software manual  | Description of CPU instruction set               | M16C/60,             | REJ09B0137    |

|                  |                                                  | M16C/20,             |               |

|                  |                                                  | M16C/Tiny Series     |               |

|                  |                                                  | Software Manual      |               |

| Application note | Information on using peripheral functions and    | Available from Re    | nesas         |

|                  | application examples                             | Technology web s     | ite           |

|                  | Sample programs                                  |                      |               |

|                  | Information on writing programs in assembly      |                      |               |

|                  | language and C                                   |                      |               |

| Renesas          | Product specifications, updates on documents,    |                      |               |

| technical update | etc.                                             |                      |               |

### 2. Notation of Numbers and Symbols

The notation conventions for register names, bit names, numbers, and symbols used in this manual are described below.

#### (1) Register Names, Bit Names, and Pin Names

Registers, bits, and pins are referred to in the text by symbols. The symbol is accompanied by the word "register," "bit," or "pin" to distinguish the three categories.

Examples the PM03 bit in the PM0 register

P3\_5 pin, VCC pin

#### (2) Notation of Numbers

The indication "b" is appended to numeric values given in binary format. However, nothing is appended to the values of single bits. The indication "h" is appended to numeric values given in hexadecimal format. Nothing is appended to numeric values given in decimal format.

Examples Binary: 11b

Hexadecimal: EFA0h

Decimal: 1234

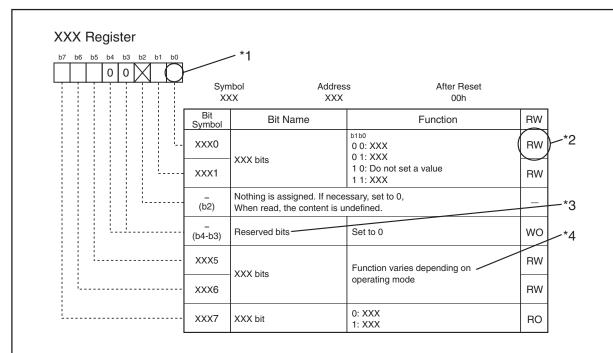

# 3. Register Notation

The symbols and terms used in register diagrams are described below.

\*1

Blank: Set to 0 or 1 according to the application

0 : Set to 0 1 : Set to 1

X: Nothing is assigned

\*2

RW: Read and write RO: Read only WO: Write only

- : Nothing is assigned

\*3

• Reserved bit

Reserved bit. Set to specified value.

\*4

· Nothing is assigned

Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.

• Do not set a value

Operation is not guaranteed when a value is set.

• Function varies depending on operating mode

The function of the bit varies with the peripheral function mode.

Refer to the register diagram for information on the individual modes.

# 4. List of Abbreviations and Acronyms

| Abbreviation | Full Form                                    |

|--------------|----------------------------------------------|

| ACIA         | Asynchronous Communication Interface Adapter |

| bps          | bits per second                              |

| CRC          | Cyclic Redundancy Check                      |

| DMA          | Direct Memory Access                         |

| DMAC         | Direct Memory Access Controller              |

| GSM          | Global System for Mobile Communications      |

| Hi-Z         | High Impedance                               |

| IEBus        | Inter Equipment bus                          |

| I/O          | Input/Output                                 |

| IrDA         | Infrared Data Association                    |

| LSB          | Least Significant Bit                        |

| MSB          | Most Significant Bit                         |

| NC           | Non-Connection                               |

| PLL          | Phase Locked Loop                            |

| PWM          | Pulse Width Modulation                       |

| SFR          | Special Function Registers                   |

| SIM          | Subscriber Identity Module                   |

| UART         | Universal Asynchronous Receiver/Transmitter  |

| VCO          | Voltage Controlled Oscillator                |

# **Table of Contents**

| SFR Page Reference                                          | B-1 |

|-------------------------------------------------------------|-----|

| 1. Overview                                                 |     |

| 1.1 Applications                                            |     |

| 1.2 Performance Overview                                    |     |

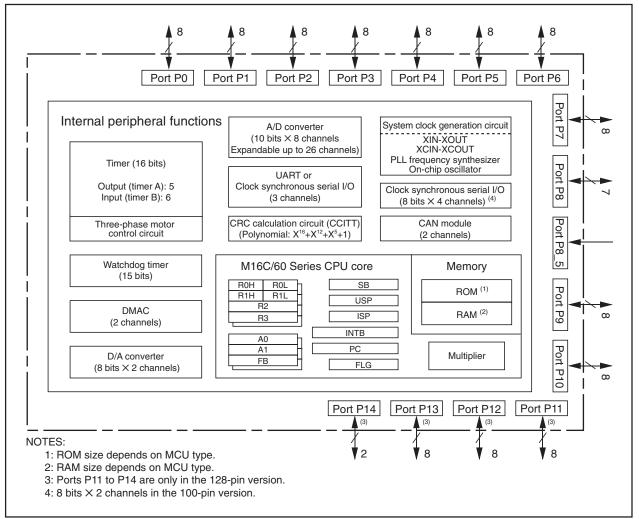

| 1.3 Block Diagram                                           | 4   |

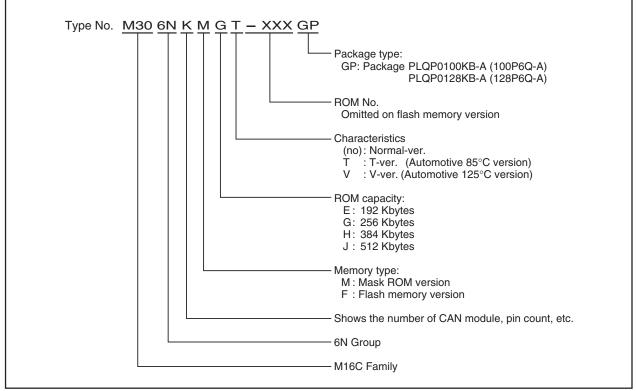

| 1.4 Product Information                                     | 5   |

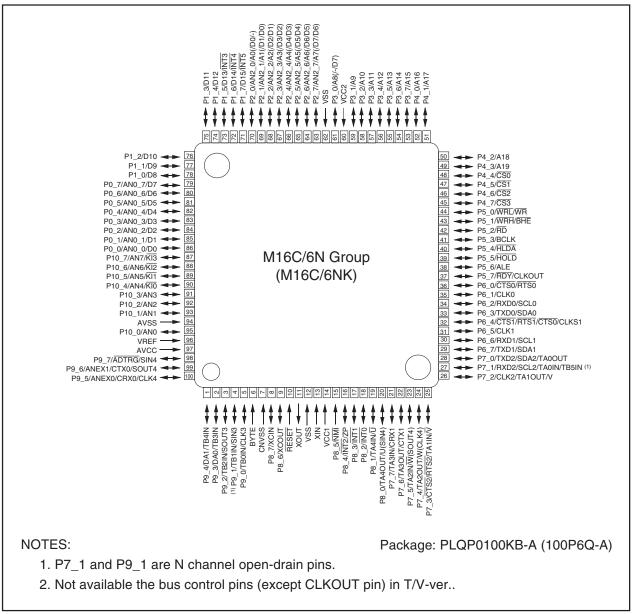

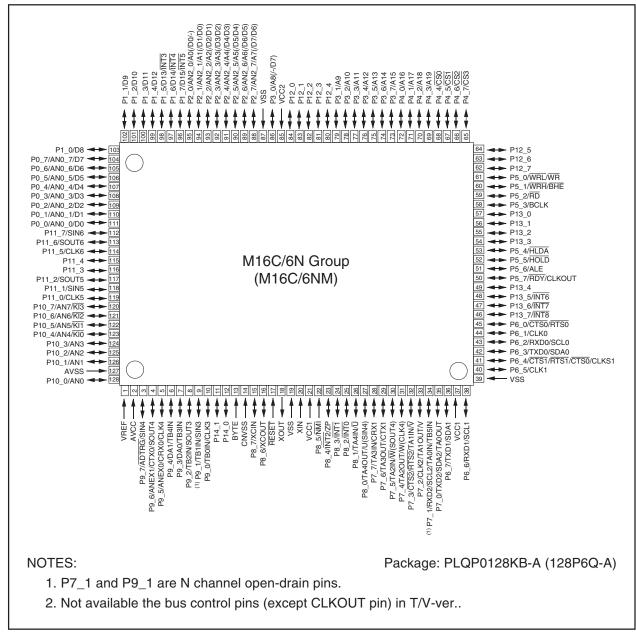

| 1.5 Pin Assignments                                         | 6   |

| 1.6 Pin Functions                                           | 13  |

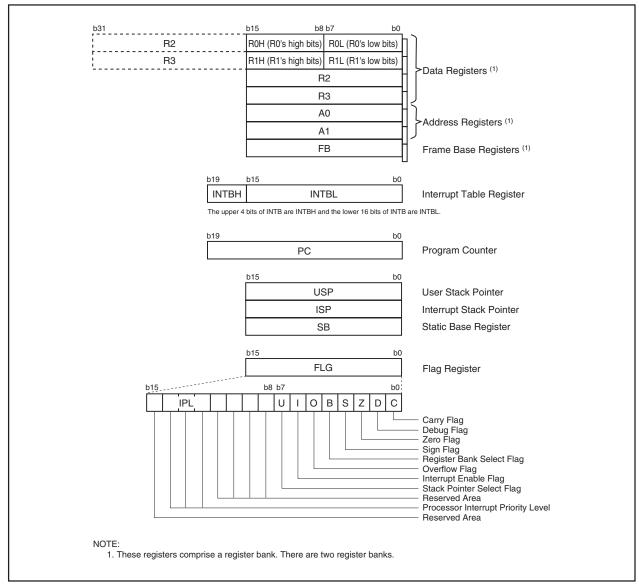

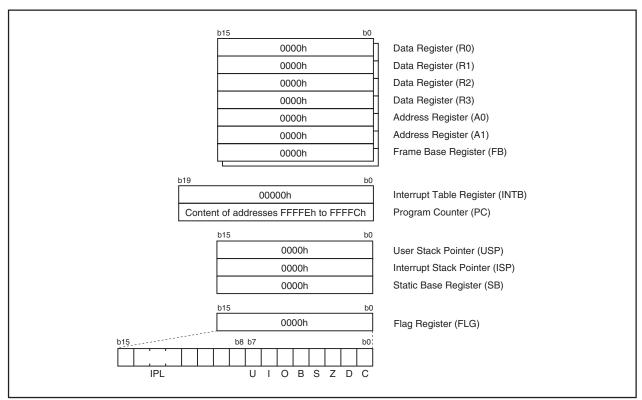

| 2. Central Processing Unit (CPU)                            | 16  |

| 2.1 Data Registers (R0, R1, R2, and R3)                     | 16  |

| 2.2 Address Registers (A0 and A1)                           | 16  |

| 2.3 Frame Base Register (FB)                                | 17  |

| 2.4 Interrupt Table Register (INTB)                         | 17  |

| 2.5 Program Counter (PC)                                    | 17  |

| 2.6 User Stack Pointer (USP), Interrupt Stack Pointer (ISP) |     |

| 2.7 Static Base Register (SB)                               | 17  |

| 2.8 Flag Register (FLG)                                     |     |

| 2.8.1 Carry Flag (C Flag)                                   |     |

| 2.8.2 Debug Flag (D Flag)                                   |     |

| 2.8.3 Zero Flag (Z Flag)                                    |     |

| 2.8.4 Sign Flag (S Flag)                                    |     |

| 2.8.5 Register Bank Select Flag (B Flag)                    |     |

| 2.8.6 Overflow Flag (O Flag)                                |     |

| 2.8.7 Interrupt Enable Flag (I Flag)                        |     |

| 2.8.8 Stack Pointer Select Flag (U Flag)                    |     |

| 2.8.9 Processor Interrupt Priority Level (IPL)              |     |

|                                                             |     |

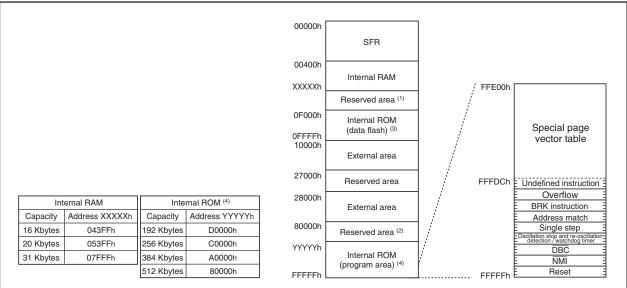

| 3. Memory                                                   |     |

| 4. Special Function Registers (SFRs)                        |     |

| 5. Resets                                                   | 35  |

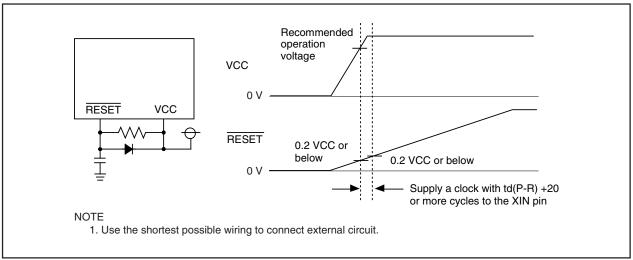

| 5.1 Hardware Reset                                          |     |

| 5.1.1 Reset on a Stable Supply Voltage                      |     |

| 5.1.2 Power-on Reset                                        |     |

| 5.2 Software Reset                                          |     |

| 5.3 Watchdog Timer Reset                                    |     |

| 5.4 Oscillation Stop Detection Reset                        |     |

| 5.5 Internal Space                                          |     |

| 6. Processor Mode                                           |     |

| 6.1 Types of Processor Mode                                 |     |

| 6.2 Setting Processor Modes                                 |     |

| 7. Bus                                                      | 45  |

| 7.1 Bus Mode                                                | 45  |

| 7.1.1 Separate Bus                                          | 45  |

| 7.1.2 Multiplexed Bus                                       | 45  |

| 7.2 Bus Control                                                       | 46  |

|-----------------------------------------------------------------------|-----|

| 7.2.1 Address Bus                                                     | 46  |

| 7.2.2 Data Bus                                                        | 46  |

| 7.2.3 Chip Select Signal                                              | 46  |

| 7.2.4 Read and Write Signals                                          | 48  |

| 7.2.5 ALE Signal                                                      |     |

| 7.2.6 RDY Signal                                                      |     |

| 7.2.7 HOLD Signal                                                     |     |

| 7.2.8 BCLK Output                                                     |     |

| 7.2.9 External Bus Status when Internal Area Accessed                 |     |

| 7.2.10 Software Wait                                                  |     |

| 8. Clock Generation Circuit                                           |     |

| 8.1 Types of Clock Generation Circuit                                 |     |

| 8.1.1 Main Clock                                                      |     |

| 8.1.2 Sub Clock                                                       |     |

| 8.1.3 On-chip Oscillator Clock                                        |     |

| 8.1.4 PLL Clock                                                       |     |

| 8.2 CPU Clock and Peripheral Function Clock                           |     |

| 8.2.1 CPU Clock and BCLK                                              |     |

| 8.2.2 Peripheral Function Clock                                       |     |

| 8.3 Clock Output Function                                             |     |

| 8.4 Power Control                                                     |     |

| 8.4.1 Normal Operating Mode                                           |     |

|                                                                       |     |

| 8.4.2 Wait Mode                                                       |     |

| 8.4.3 Stop Mode                                                       |     |

| 8.5 Oscillation Stop and Re-oscillation Detection Function            |     |

| 8.5.1 Operation when CM27 Bit = 0 (Oscillation Stop Detection Rese    |     |

| 8.5.2 Operation when CM27 Bit = 1 (Oscillation Stop, Re-oscillation I | • / |

| 8.5.3 How to Use Oscillation Stop and Re-oscillation Detection Func   |     |

| 9. Protection                                                         | 80  |

| 10. Interrupts                                                        | 81  |

| 10.1 Type of Interrupts                                               | 81  |

| 10.2 Software Interrupts                                              | 82  |

| 10.2.1 Undefined Instruction Interrupt                                | 82  |

| 10.2.2 Overflow Interrupt                                             | 82  |

| 10.2.3 BRK Interrupt                                                  | 82  |

| 10.2.4 INT Instruction Interrupt                                      | 82  |

| 10.3 Hardware Interrupts                                              | 83  |

| 10.3.1 Special Interrupts                                             | 83  |

| 10.3.2 Peripheral Function Interrupts                                 |     |

| 10.4 Interrupts and Interrupt Vector                                  |     |

| 10.4.1 Fixed Vector Tables                                            |     |

| 10.4.2 Relocatable Vector Tables                                      |     |

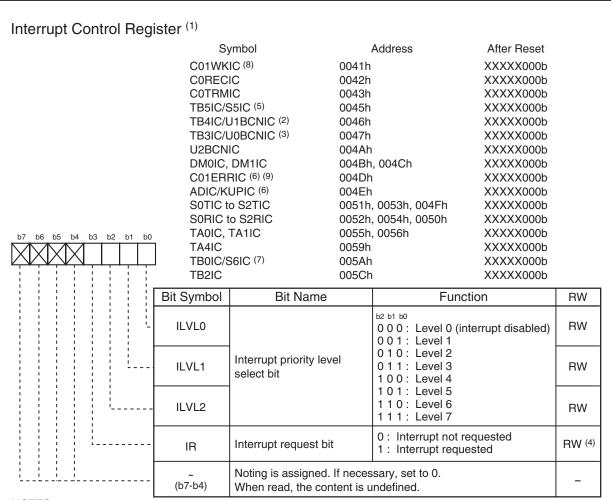

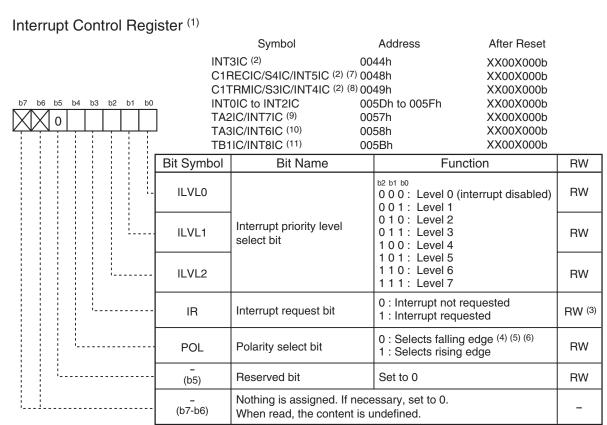

| 10.5 Interrupt Control                                                |     |

| 10.5.1   Flag                                                         |     |

| 10.5.2 IR Bit                                                         |     |

| 10.5.3 Rits II VI 2 to II VI 0 and IPI                                | 88  |

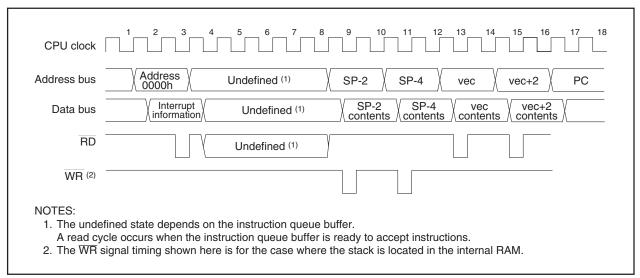

| 10.5.4 Interrupt Sequence                                  | 89  |

|------------------------------------------------------------|-----|

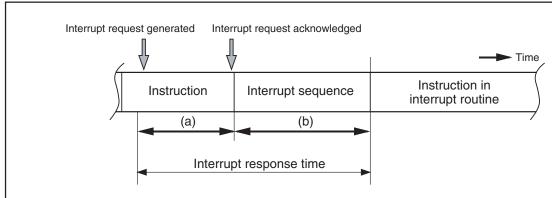

| 10.5.5 Interrupt Response Time                             | 90  |

| 10.5.6 Variation of IPL when Interrupt Request is Accepted | 90  |

| 10.5.7 Saving Registers                                    | 91  |

| 10.5.8 Returning from Interrupt Routine                    | 92  |

| 10.5.9 Interrupt Priority                                  | 92  |

| 10.5.10 Interrupt Priority Level Select Circuit            | 92  |

| 10.6 INT Interrupt                                         | 94  |

| 10.7 NMI Interrupt                                         |     |

| 10.8 Key Input Interrupt                                   | 98  |

| 10.9 CAN0/1 Wake-up Interrupt                              | 98  |

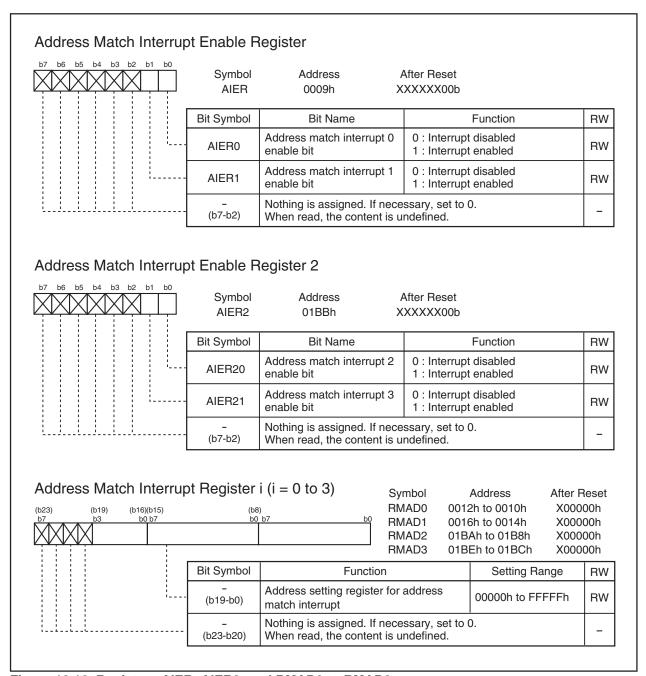

| 10.10 Address Match Interrupt                              | 99  |

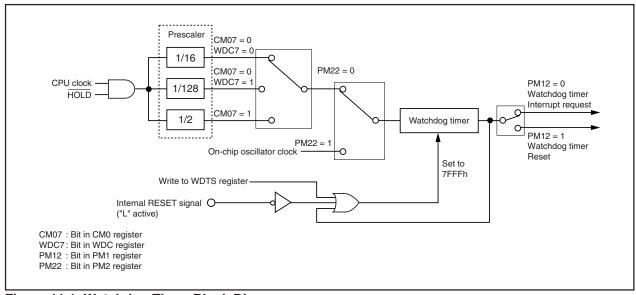

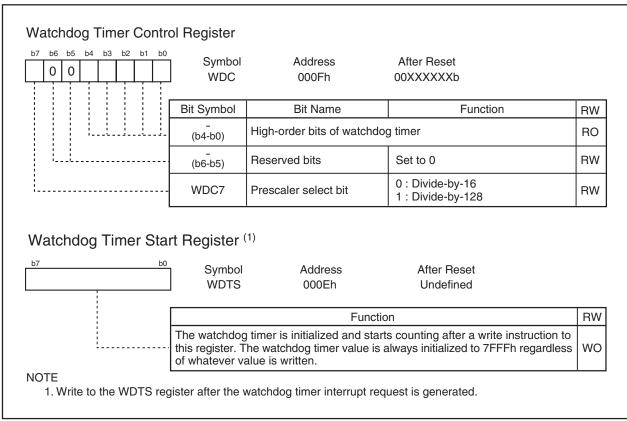

| 11. Watchdog Timer                                         | 101 |

| 11.1 Count Source Protective Mode                          | 102 |

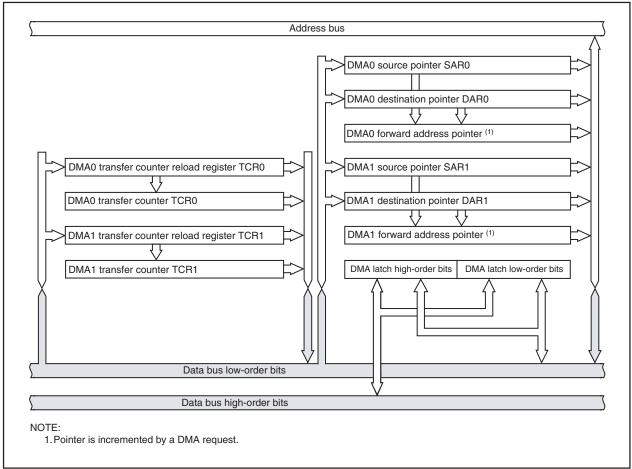

| 12. DMAC                                                   | 103 |

| 12.1 Transfer Cycle                                        | 108 |

| 12.1.1 Effect of Source and Destination Addresses          | 108 |

| 12.1.2 Effect of BYTE Pin Level                            | 108 |

| 12.1.3 Effect of Software Wait                             | 108 |

| 12.1.4 Effect of RDY Signal                                | 108 |

| 12.2 DMA Transfer Cycles                                   | 110 |

| 12.3 DMA Enable                                            | 111 |

| 12.4 DMA Request                                           | 111 |

| 12.5 Channel Priority and DMA Transfer Timing              | 112 |

| 13. Timers                                                 | 113 |

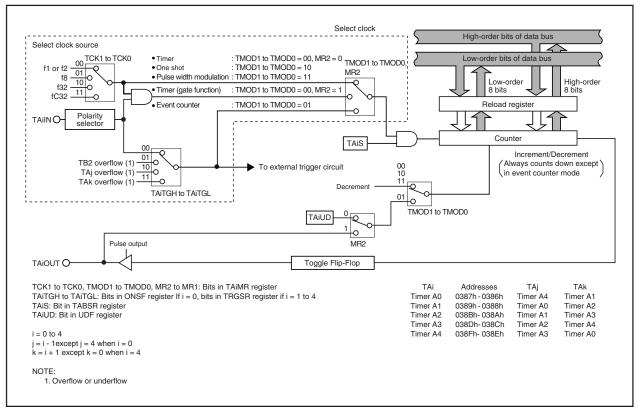

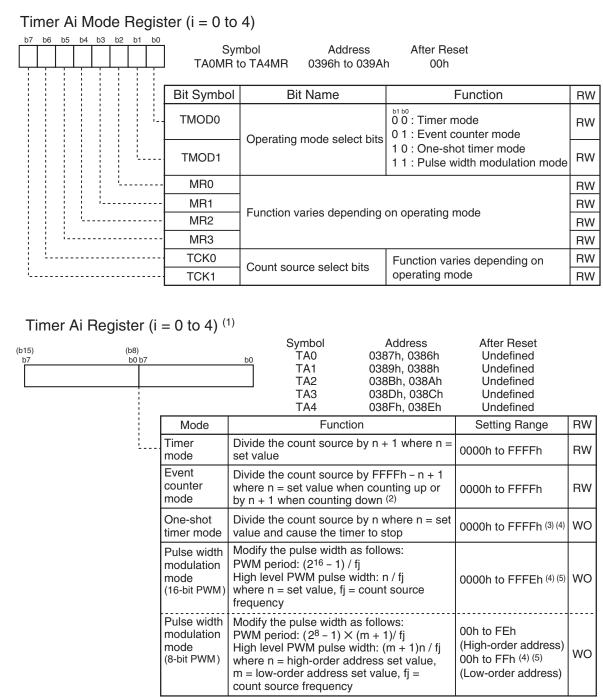

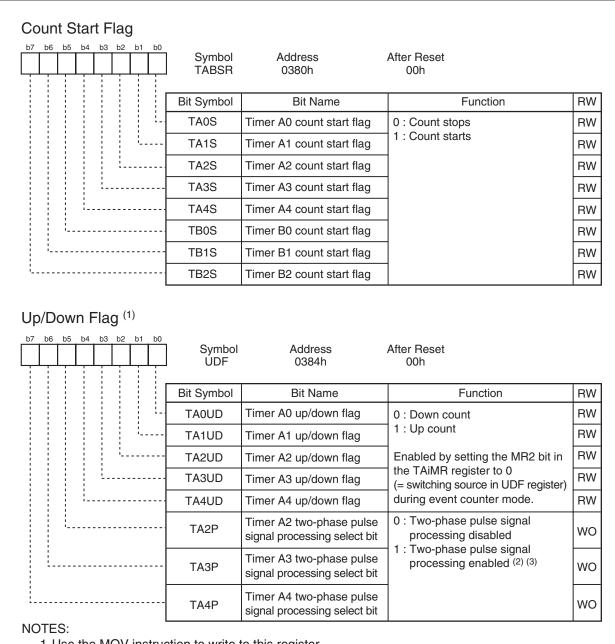

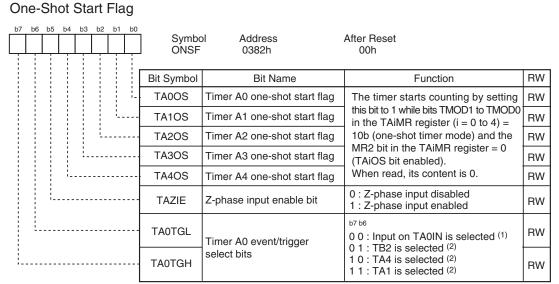

| 13.1 Timer A                                               | 115 |

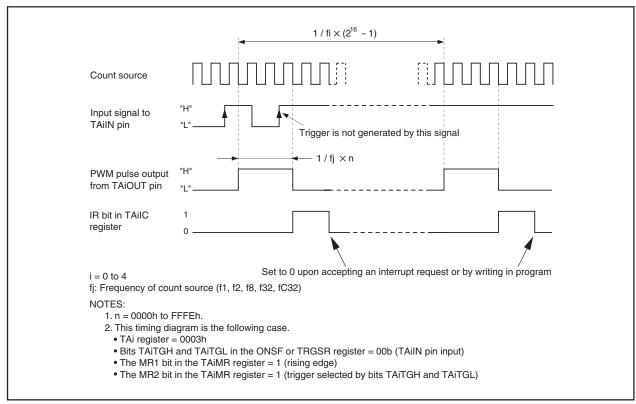

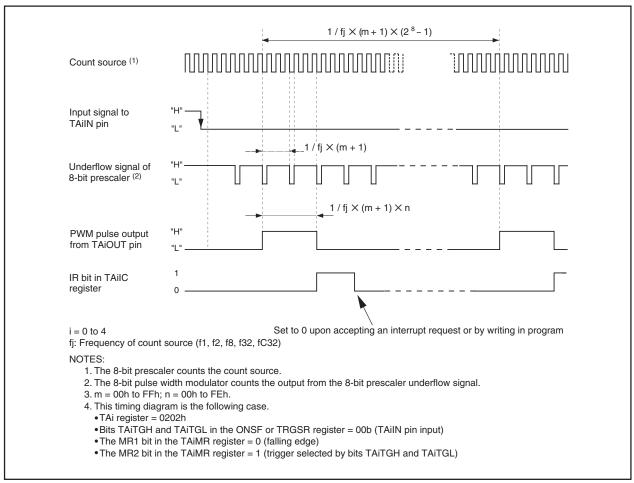

| 13.1.1 Timer Mode                                          | 119 |

| 13.1.2 Event Counter Mode                                  | 120 |

| 13.1.3 One-shot Timer Mode                                 | 125 |

| 13.1.4 Pulse Width Modulation (PWM) Mode                   | 127 |

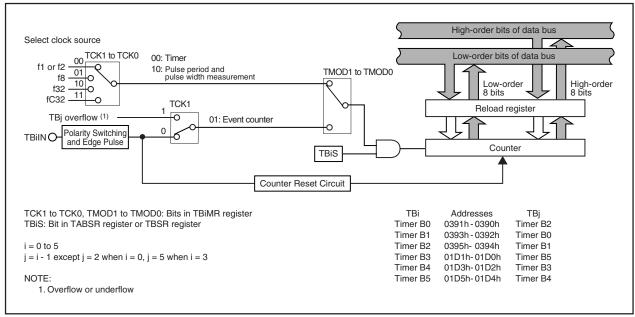

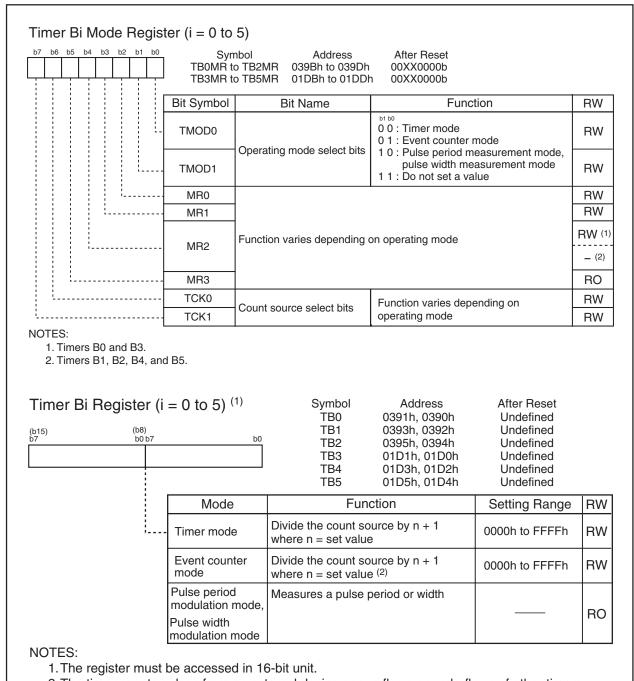

| 13.2 Timer B                                               | 130 |

| 13.2.1 Timer Mode                                          | 133 |

| 13.2.2 Event Counter Mode                                  | 134 |

| 13.2.3 Pulse Period and Pulse Width Measurement Mode       | 135 |

| 14. Three-Phase Motor Control Timer Function               | 138 |

| 15. Serial Interface                                       | 149 |

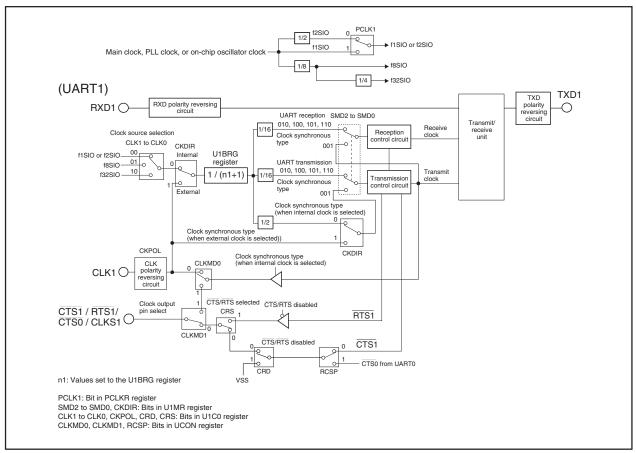

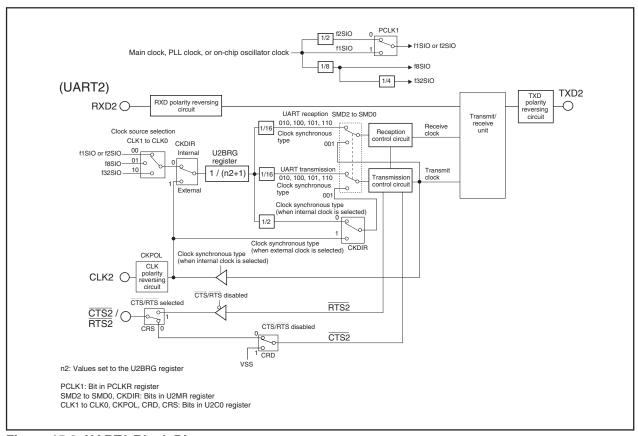

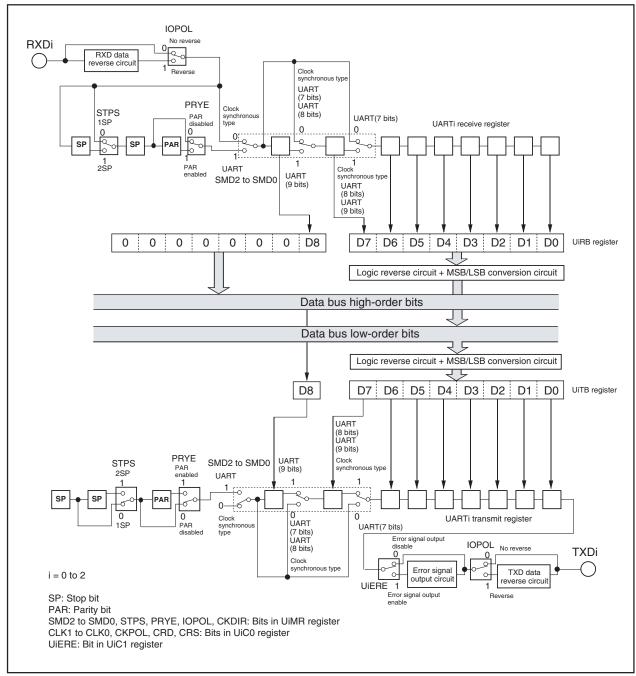

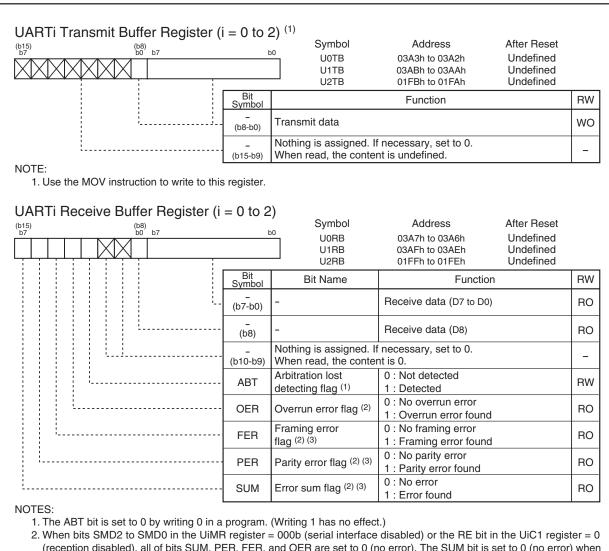

| 15.1 UARTi                                                 | 149 |

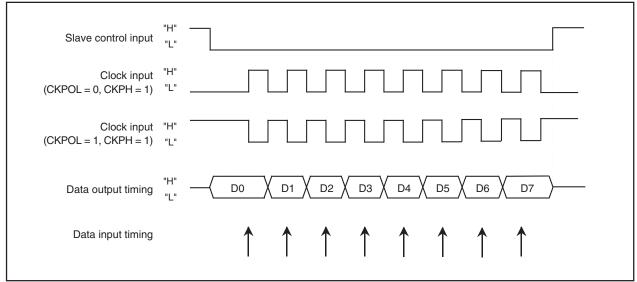

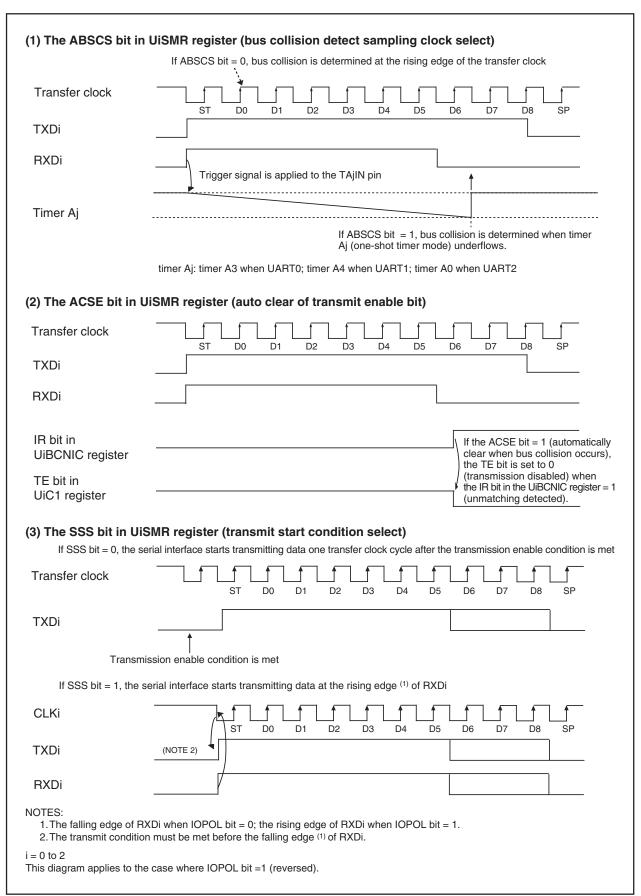

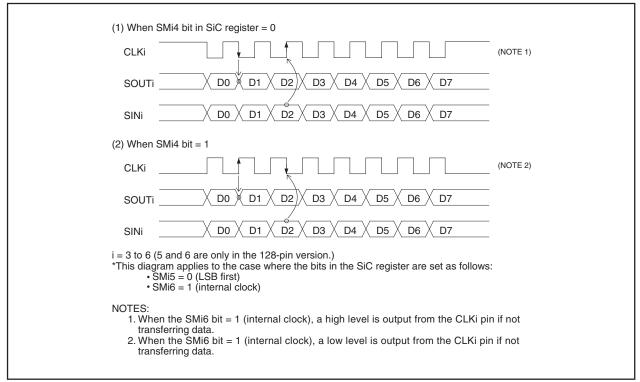

| 15.1.1 Clock Synchronous Serial I/O Mode                   | 159 |

| 15.1.2 Clock Asynchronous Serial I/O (UART) Mode           |     |

| 15.1.3 Special Mode 1 (I <sup>2</sup> C Mode)              |     |

| 15.1.4 Special Mode 2                                      |     |

| 15.1.5 Special Mode 3 (IE Mode)                            |     |

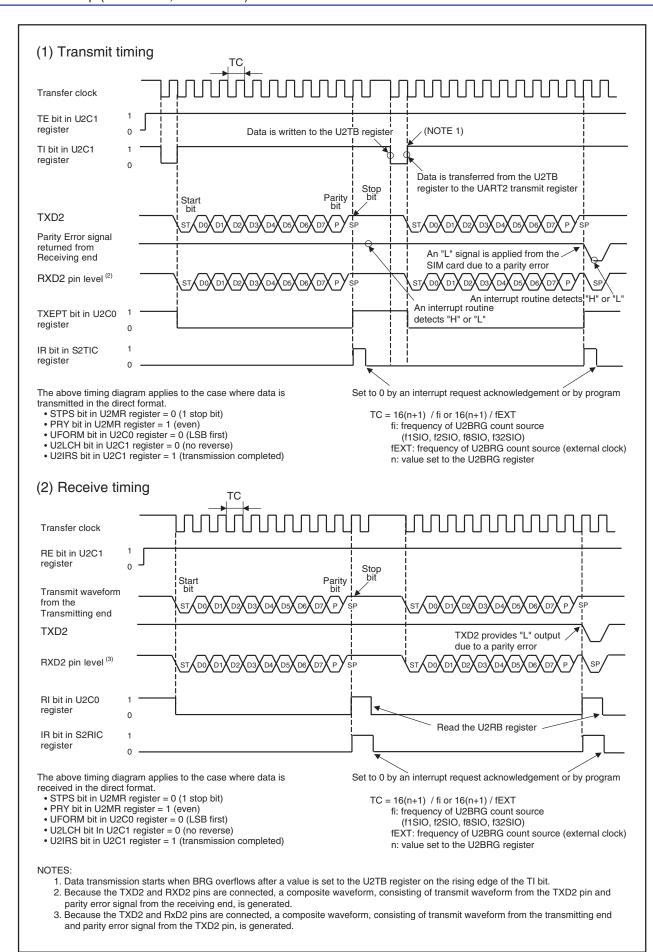

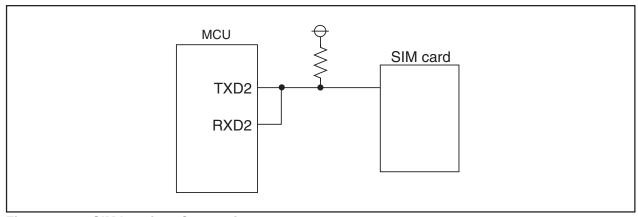

| 15.1.6 Special Mode 4 (SIM Mode) (UART2)                   |     |

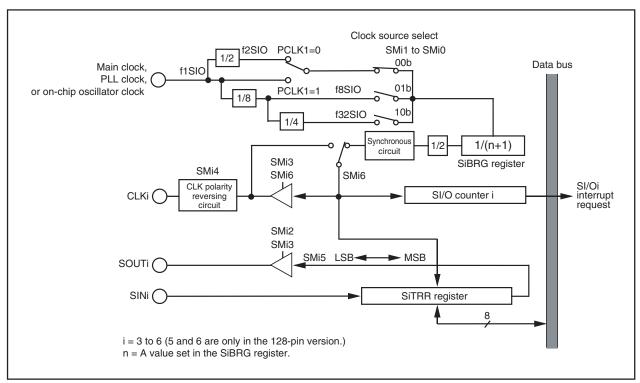

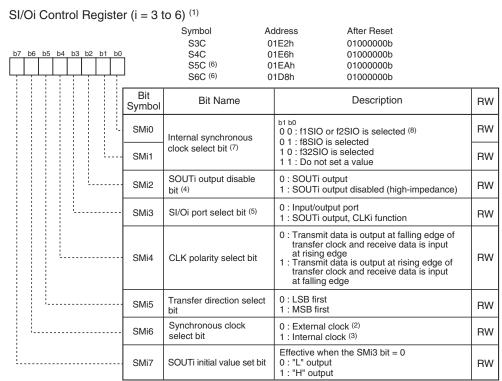

| 15.2 SI/Oi                                                 |     |

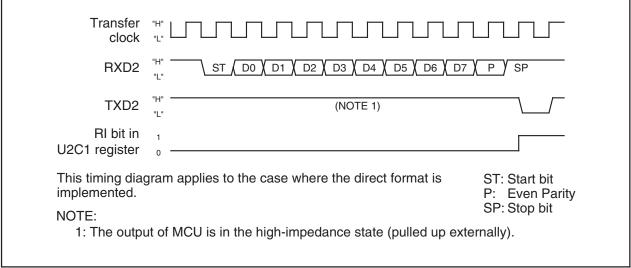

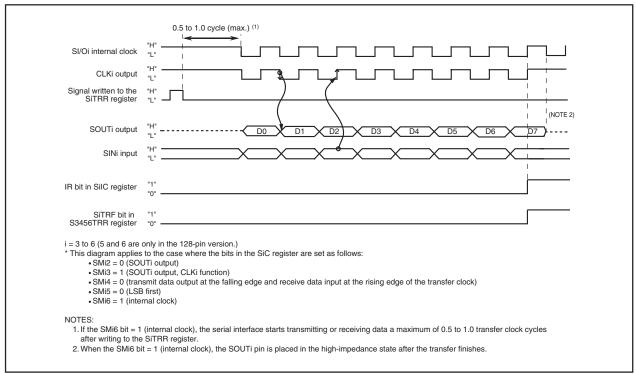

| 15.2.1 SI/Oi Operation Timing                              | 200 |

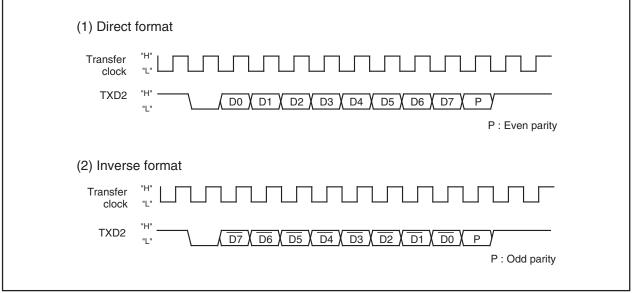

| 15.2.2 CLK Polarity Selection                              | 200 |

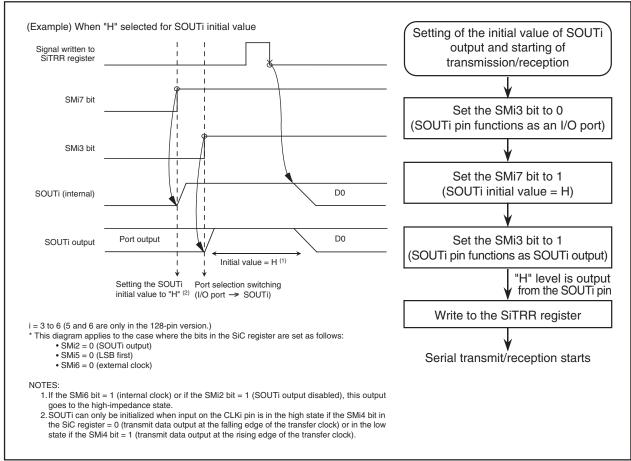

| 15.2.3 Functions for Setting an SOUTi Initial Value        | 201 |

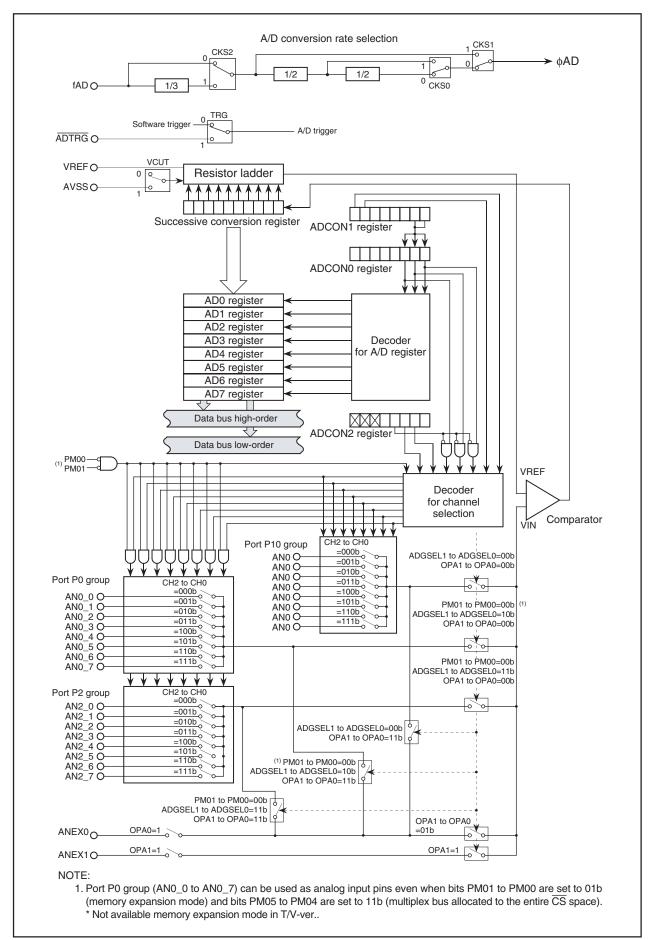

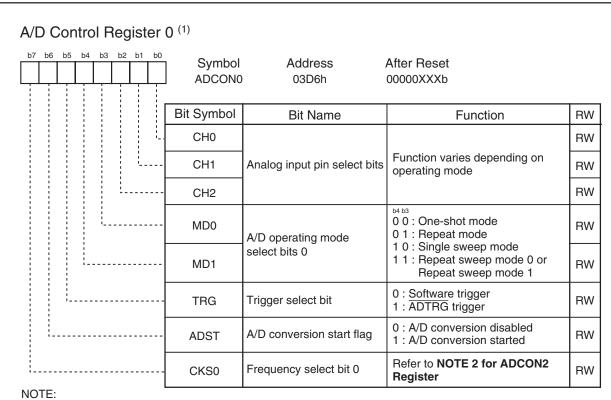

| 16. A/D Converter                                            | 202 |

|--------------------------------------------------------------|-----|

| 16.1 Mode Description                                        | 206 |

| 16.1.1 One-shot Mode                                         | 206 |

| 16.1.2 Repeat Mode                                           | 208 |

| 16.1.3 Single Sweep Mode                                     | 210 |

| 16.1.4 Repeat Sweep Mode 0                                   | 212 |

| 16.1.5 Repeat Sweep Mode 1                                   | 214 |

| 16.2 Function                                                | 216 |

| 16.2.1 Resolution Select Function                            | 216 |

| 16.2.2 Sample and Hold                                       | 216 |

| 16.2.3 Extended Analog Input Pins                            | 216 |

| 16.2.4 External Operation Amplifier (Op-Amp) Connection Mode | 216 |

| 16.2.5 Current Consumption Reducing Function                 | 217 |

| 16.2.6 Output Impedance of Sensor under A/D Conversion       | 217 |

| 17. D/A Converter                                            | 219 |

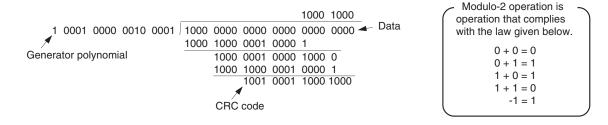

| 18. CRC Calculation                                          |     |

|                                                              |     |

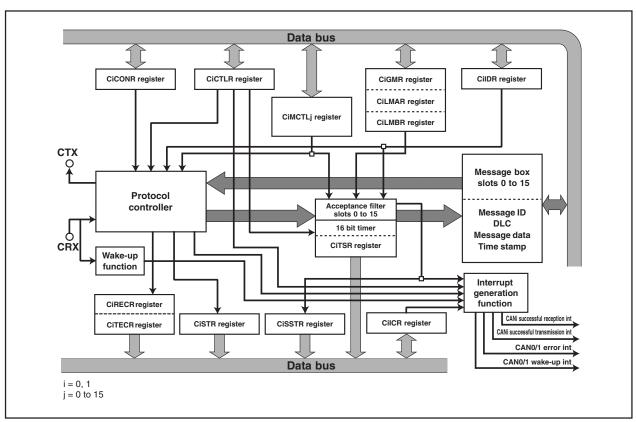

| 19. CAN Module                                               | 223 |

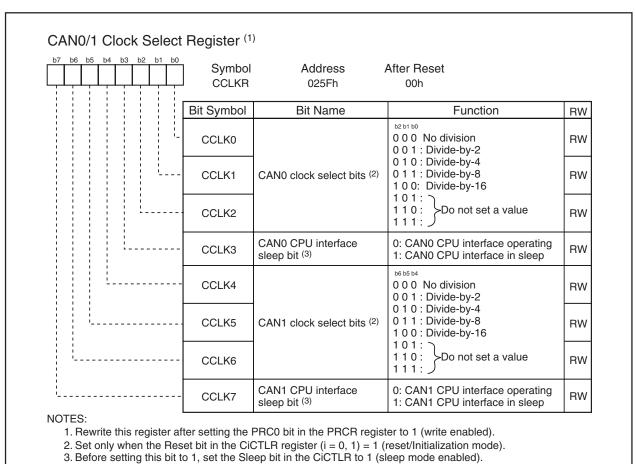

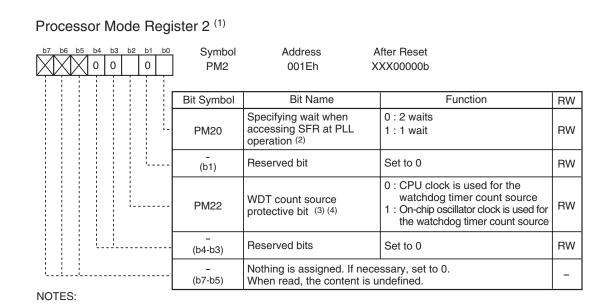

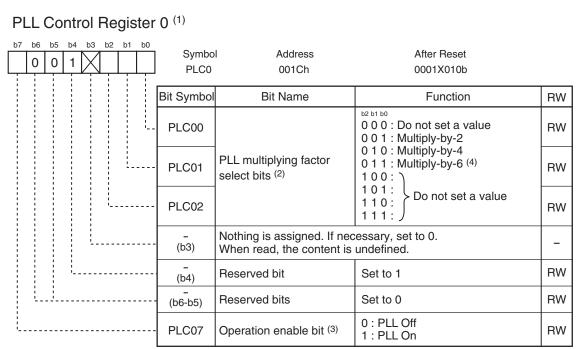

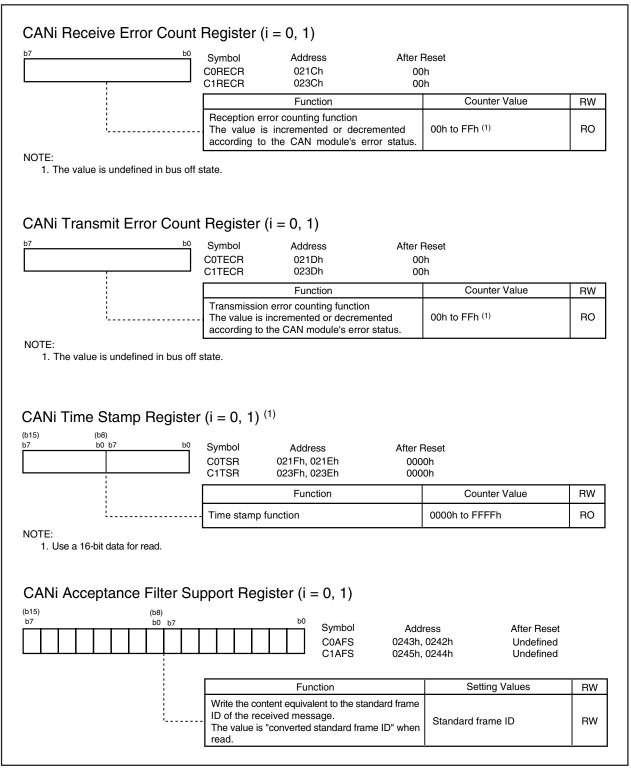

| 19.1 CAN Module-Related Registers                            | 224 |

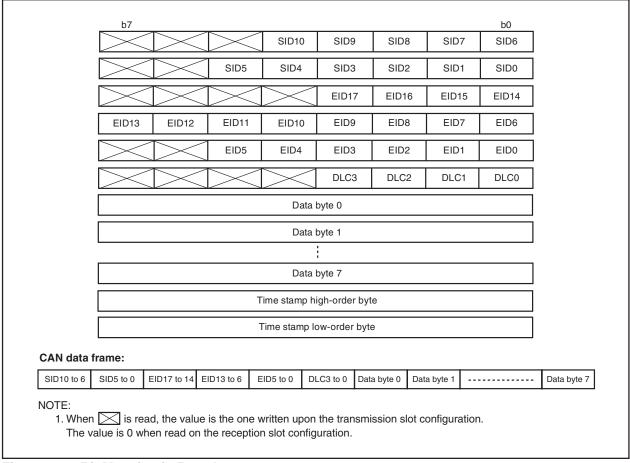

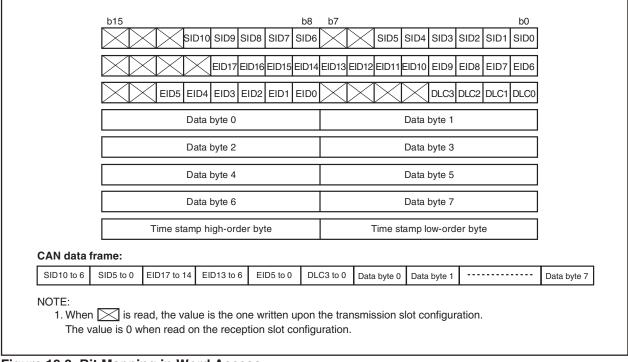

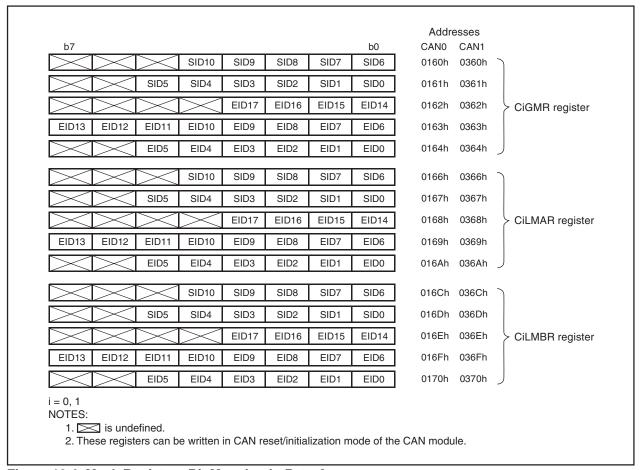

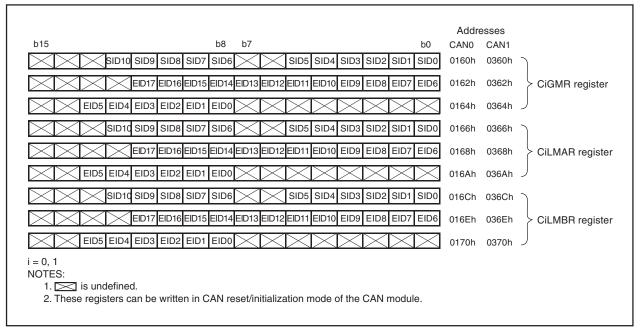

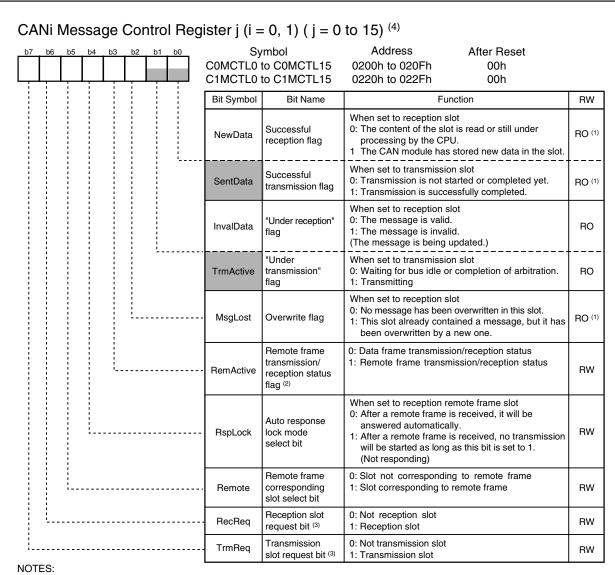

| 19.1.1 CANi Message Box                                      |     |

| 19.1.2 Acceptance Mask Registers                             | 224 |

| 19.1.3 CAN SFR Registers                                     | 224 |

| 19.2 CANi Message Box                                        |     |

| 19.3 Acceptance Mask Registers                               | 227 |

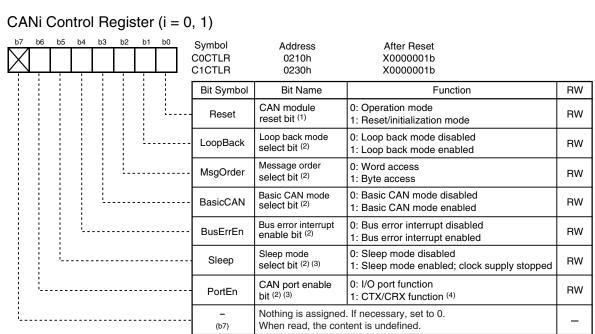

| 19.4 CAN SFR Registers                                       | 228 |

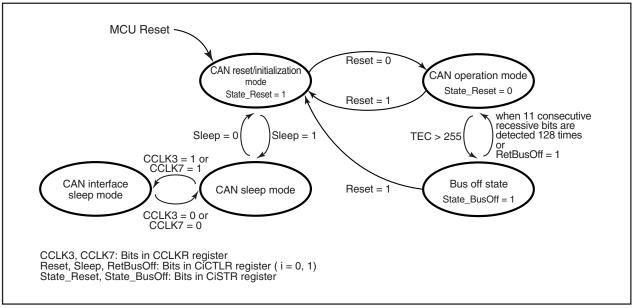

| 19.5 Operational Modes                                       |     |

| 19.5.1 CAN Reset/Initialization Mode                         | 234 |

| 19.5.2 CAN Operation Mode                                    |     |

| 19.5.3 CAN Sleep Mode                                        | 235 |

| 19.5.4 CAN Interface Sleep Mode                              | 235 |

| 19.5.5 Bus Off State                                         |     |

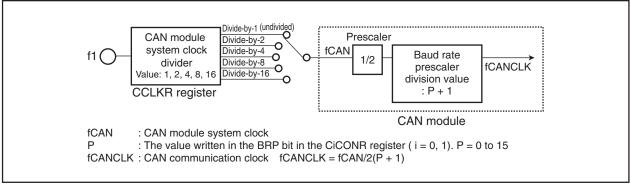

| 19.6 CAN Module System Clock Configuration                   | 237 |

| 19.7 Bit Timing Configuration                                |     |

| 19.8 Bit-rate                                                |     |

| 19.8.1 Calculation of Bit-rate                               | 238 |

| 19.9 Acceptance Filtering Function and Masking Function      | 239 |

| 19.10 Acceptance Filter Support Unit (ASU)                   |     |

| 19.11 Basic CAN Mode                                         | 241 |

| 19.12 Return from Bus Off Function                           | 242 |

| 19.13 Time Stamp Counter and Time Stamp Function             | 242 |

| 19.14 Listen-Only Mode                                       | 242 |

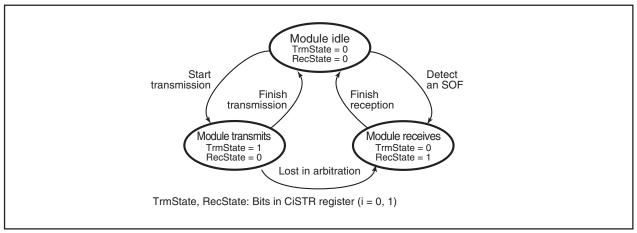

| 19.15 Reception and Transmission                             | 243 |

| 19.15.1 Reception                                            | 244 |

| 19.15.2 Transmission                                         | 245 |

| 19.16 CAN Interrupt                                          | 246 |

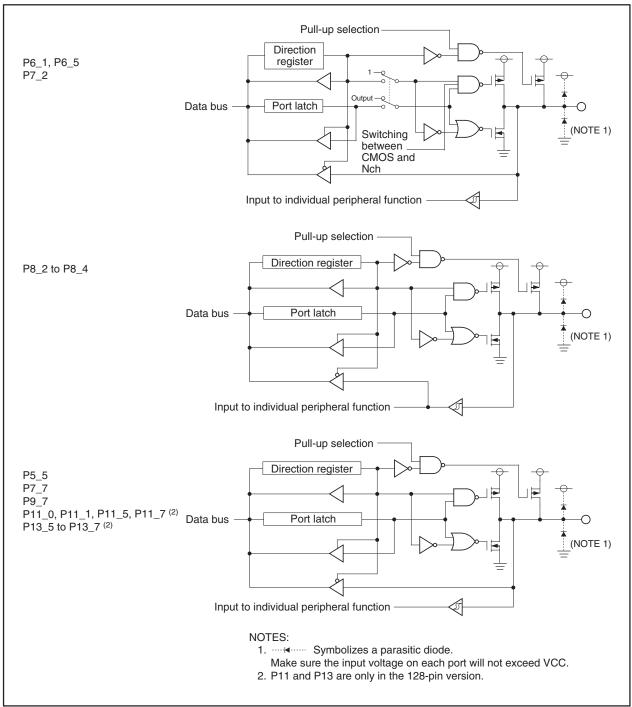

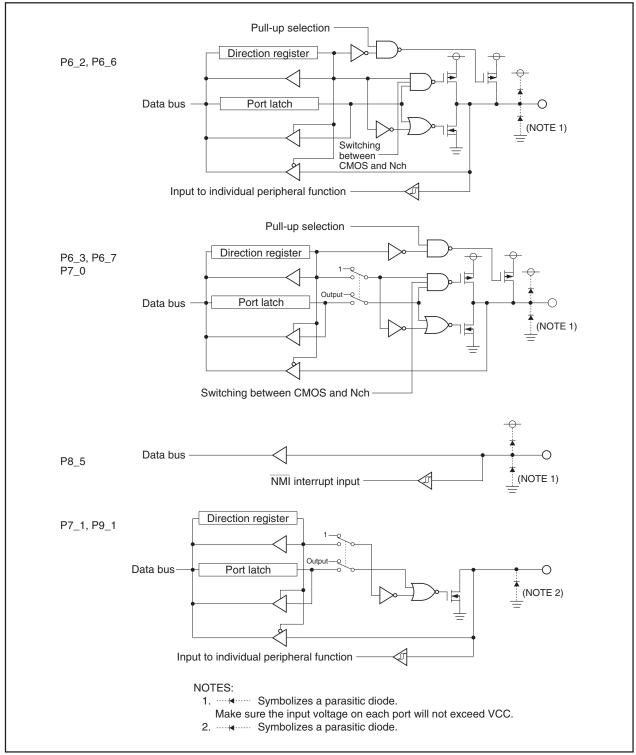

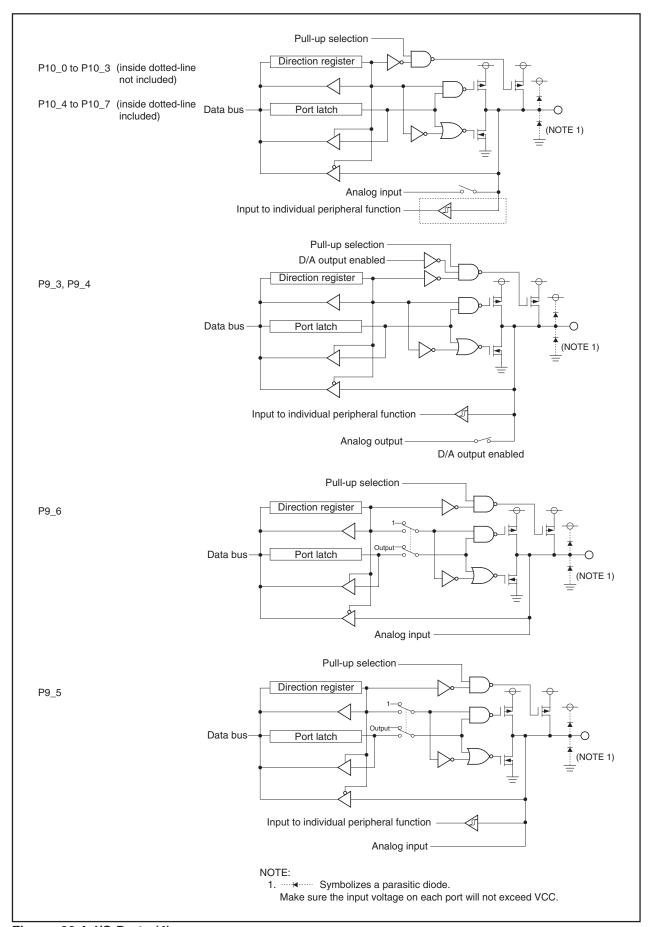

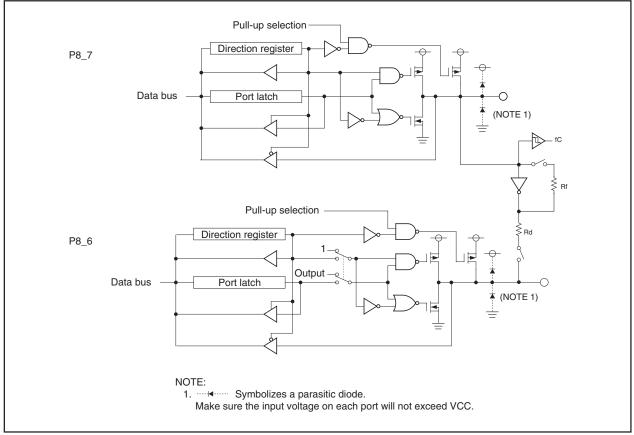

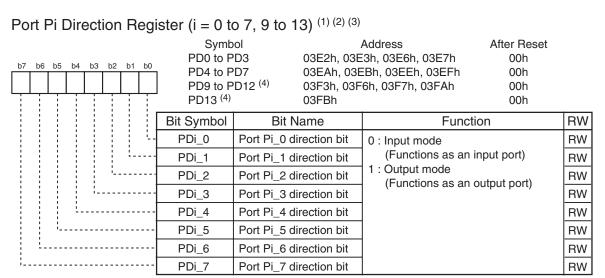

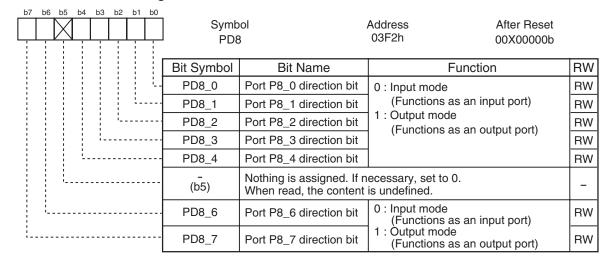

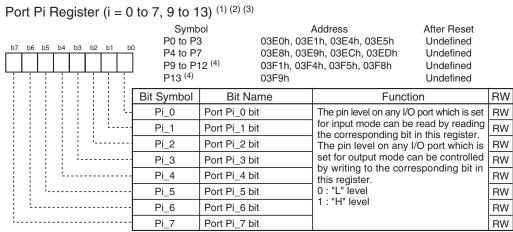

| 20. Programmable I/O Ports                                   | 247 |

| 20.1 PDi Register                                            |     |

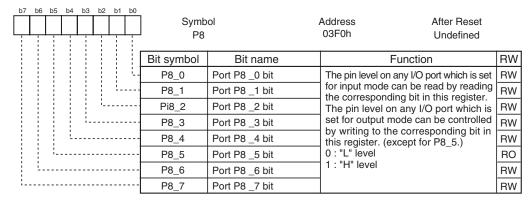

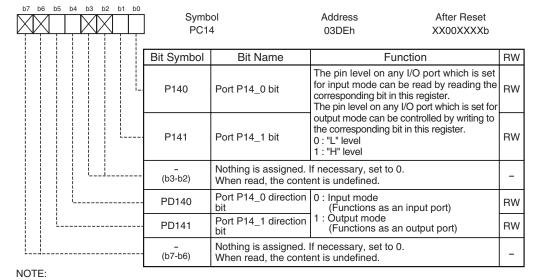

| 20.2 Pi Register, PC14 Register                              |     |

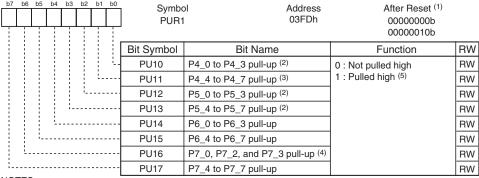

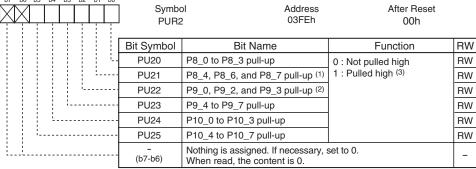

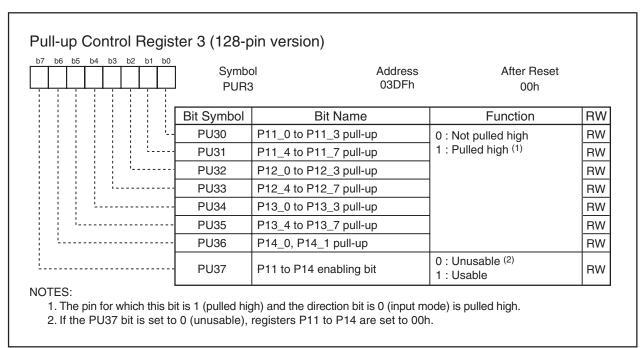

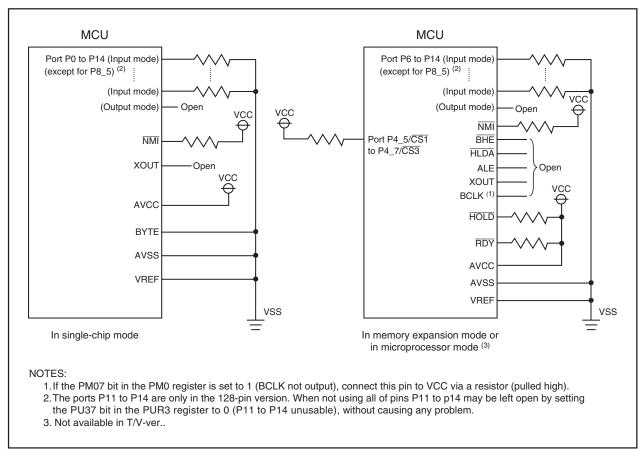

| 20.3 PURj Register                                           |     |

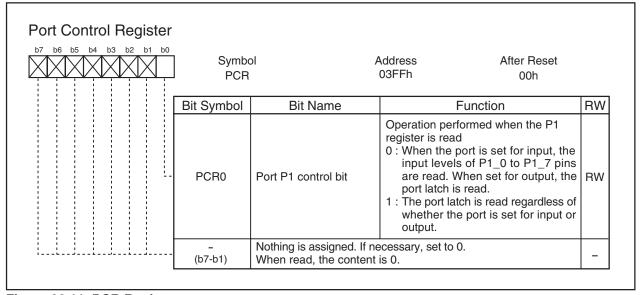

| 20.4 PCR Register                                            |     |

| 21. Flash Memory Version                                          | 260 |

|-------------------------------------------------------------------|-----|

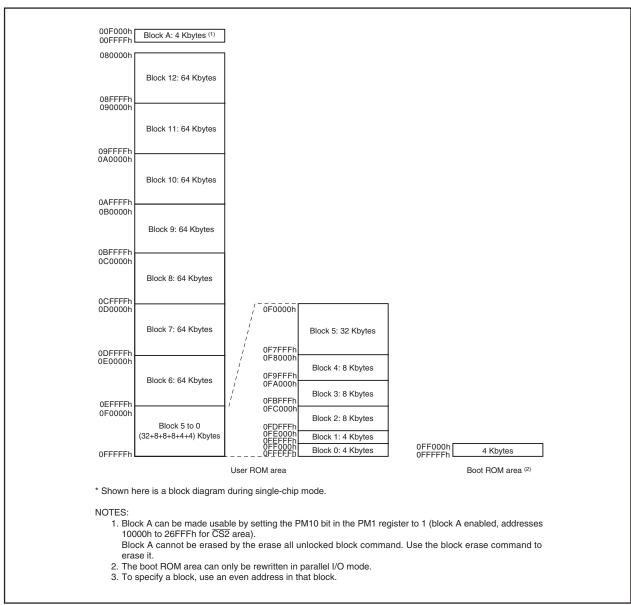

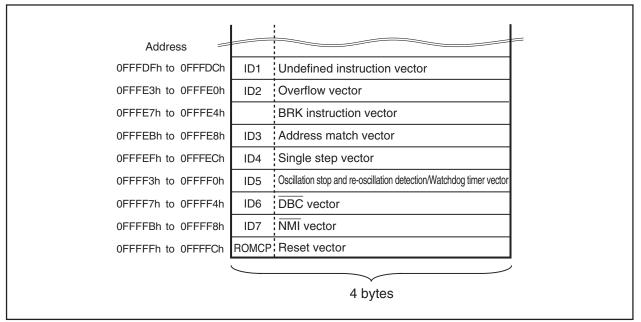

| 21.1 Memory Map                                                   | 261 |

| 21.1.1 Boot Mode                                                  | 262 |

| 21.2 Functions to Prevent Flash Memory from Rewriting             | 262 |

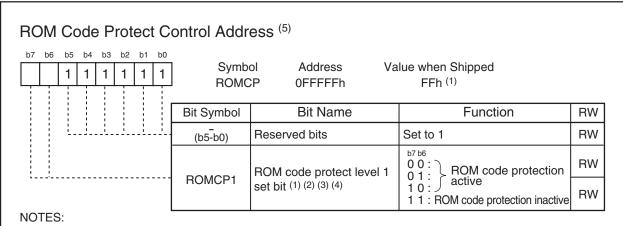

| 21.2.1 ROM Code Protect Function                                  | 262 |

| 21.2.2 ID Code Check Function                                     | 262 |

| 21.3 CPU Rewrite Mode                                             | 264 |

| 21.3.1 EW0 Mode                                                   | 265 |

| 21.3.2 EW1 Mode                                                   |     |

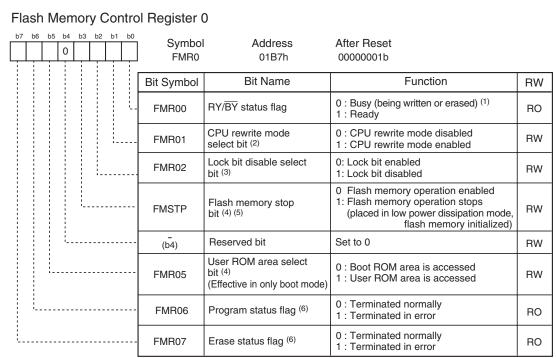

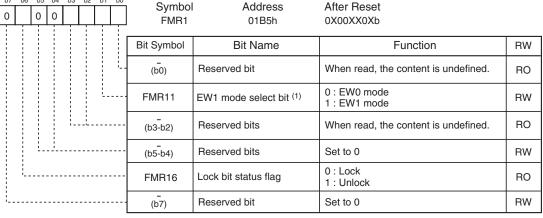

| 21.3.3 Registers FMR0 and FMR1                                    | 266 |

| 21.3.4 Notes on CPU Rewrite Mode                                  |     |

| 21.3.5 Software Commands                                          |     |

| 21.3.6 Data Protect Function                                      |     |

| 21.3.7 Status Register (SRD Register)                             |     |

| 21.3.8 Full Status Check                                          |     |

| 21.4 Standard Serial I/O Mode                                     |     |

| 21.4.1 ID Code Check Function                                     |     |

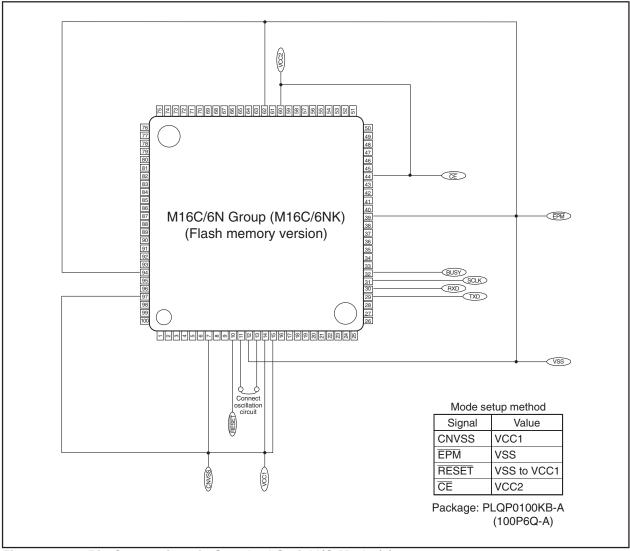

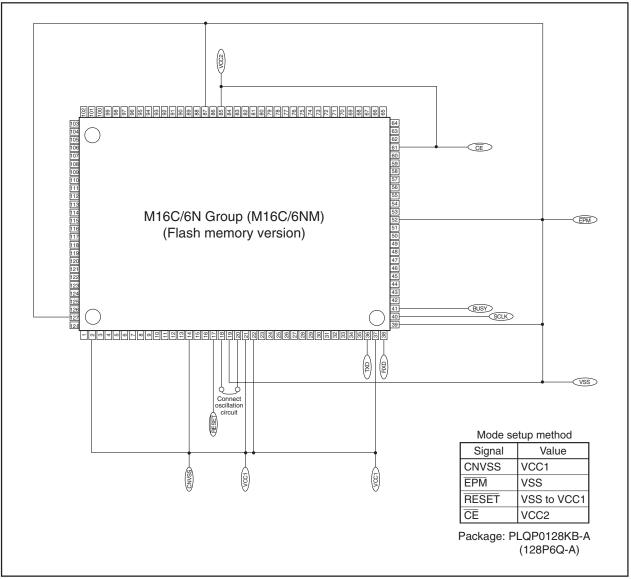

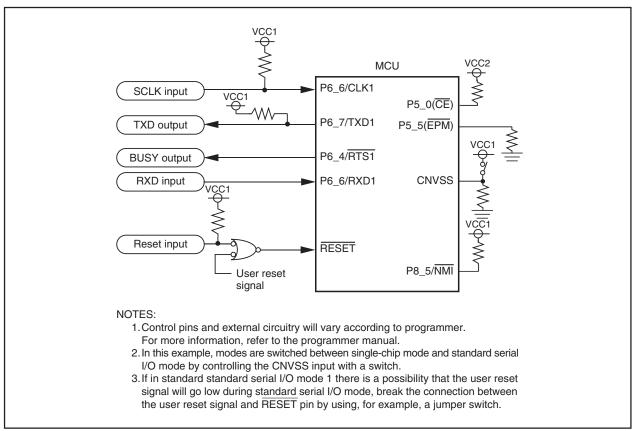

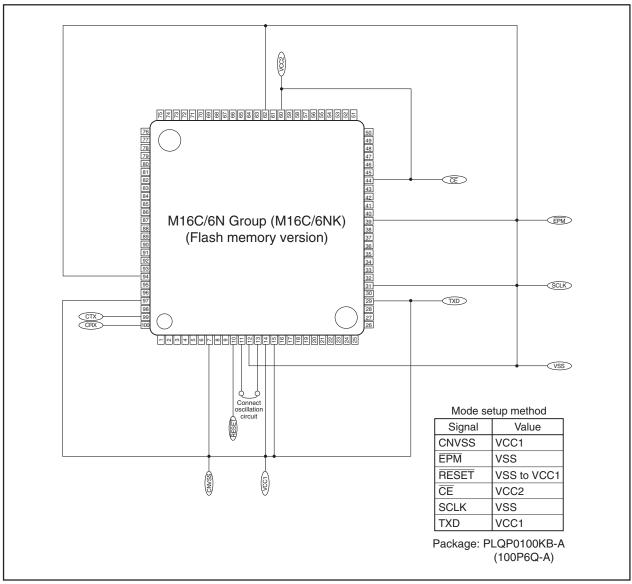

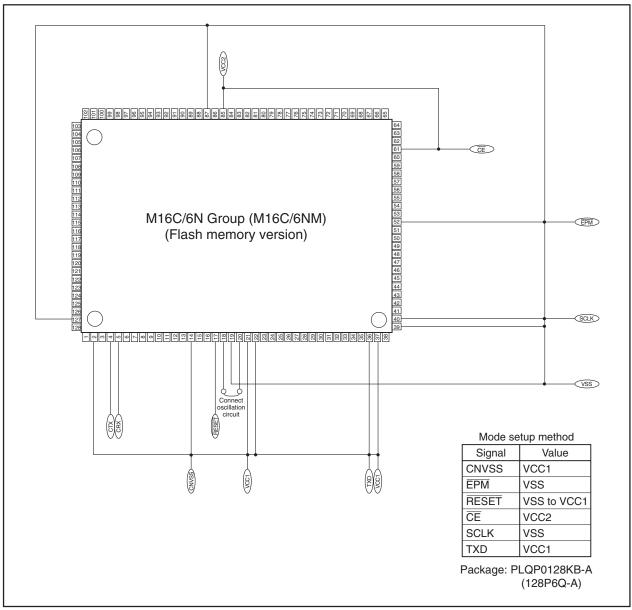

| 21.4.2 Example of Circuit Application in Standard Serial I/O Mode |     |

| 21.5 Parallel I/O Mode                                            |     |

| 21.5.1 User ROM and Boot ROM Areas                                |     |

| 21.5.2 ROM Code Protect Function                                  |     |

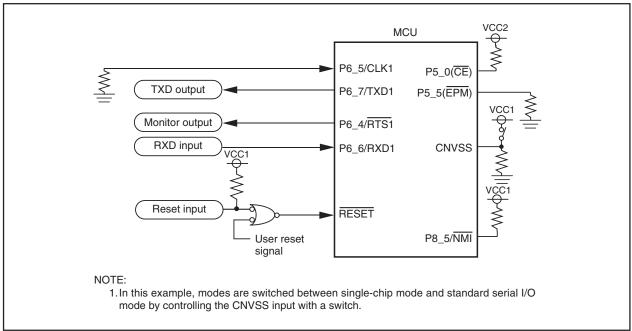

| 21.6 CAN I/O Mode                                                 |     |

| 21.6.1 ID Code Check Function                                     |     |

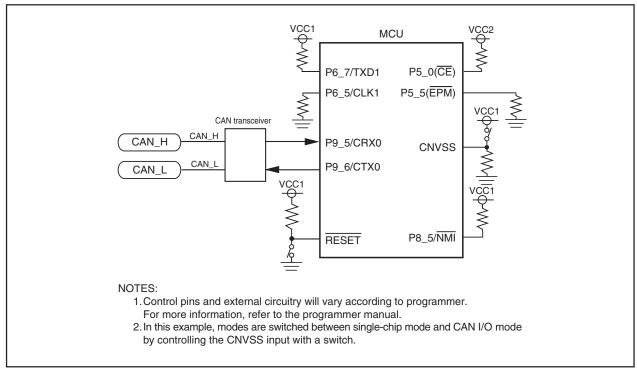

| 21.6.2 Example of Circuit Application in CAN I/O Mode             |     |

| 22. Electrical Characteristics                                    |     |

| 22.1 Electrical Characteristics (Normal-ver.)                     |     |

| 22.2 Electrical Characteristics (T/V-ver.)                        | 328 |

| 23. Usage Notes                                                   | 338 |

| 23.1 SFRs                                                         | 338 |

| 23.2 External Bus (Normal-ver. only)                              | 339 |

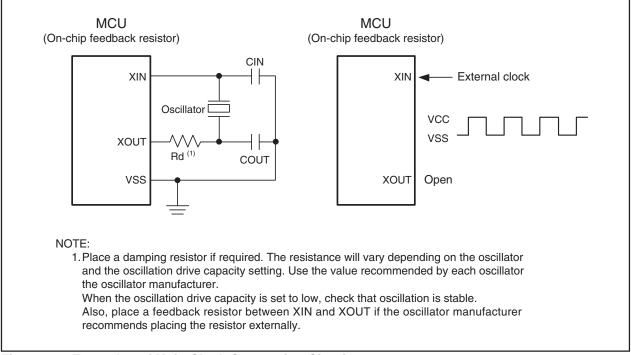

| 23.3 External Clock                                               | 340 |

| 23.4 PLL Frequency Synthesizer                                    | 341 |

| 23.5 Power Control                                                | 342 |

| 23.6 Oscillation Stop, Re-oscillation Detection Function          | 344 |

| 23.7 Protection                                                   | 345 |

| 23.8 Interrupts                                                   | 346 |

| 23.8.1 Reading Address 00000h                                     | 346 |

| 23.8.2 Setting SP                                                 |     |

| 23.8.3 NMI Interrupt                                              | 346 |

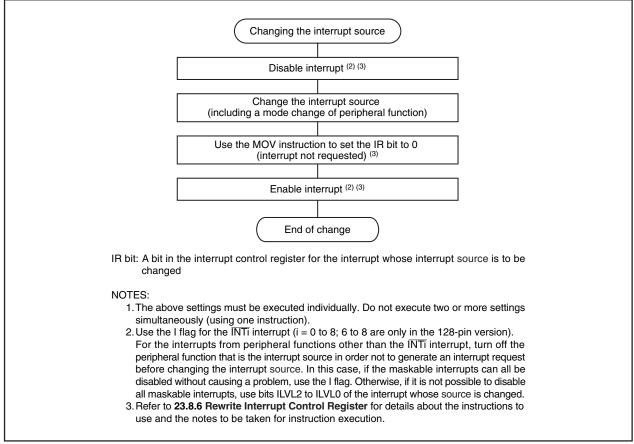

| 23.8.4 Changing Interrupt Source                                  |     |

| 23.8.5 INT Interrupt                                              | 347 |

| 23.8.6 Rewrite Interrupt Control Register                         |     |

| 23.8.7 Watchdog Timer Interrupt                                   |     |

| 23.9 DMAC                                                         |     |

| 23.9.1 Write to DMAE Bit in DMiCON Register                       |     |

| 23.10 Timers                                                      |     |

| 23.10.1 Timer A                                                   |     |

| 23.10.2 Timer B                                                   | 354 |

| 23.11 Thee-Phase Motor Control Timer Function                                              | 356 |

|--------------------------------------------------------------------------------------------|-----|

| 23.12 Serial Interface                                                                     | 357 |

| 23.12.1 Clock Synchronous Serial I/O Mode                                                  | 357 |

| 23.12.2 Special Modes                                                                      | 358 |

| 23.12.3 SI/Oi                                                                              | 359 |

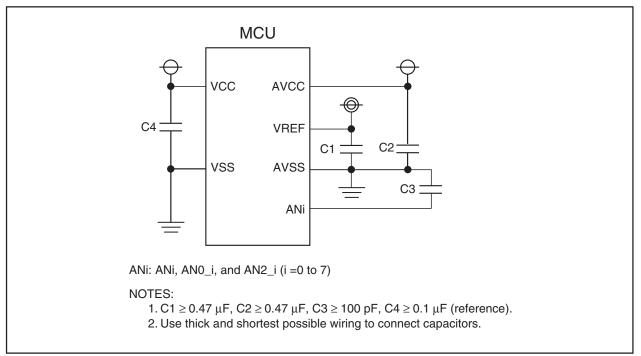

| 23.13 A/D Converter                                                                        | 360 |

| 23.14 CAN Module                                                                           | 362 |

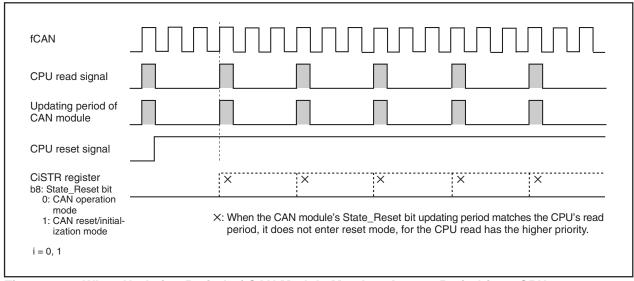

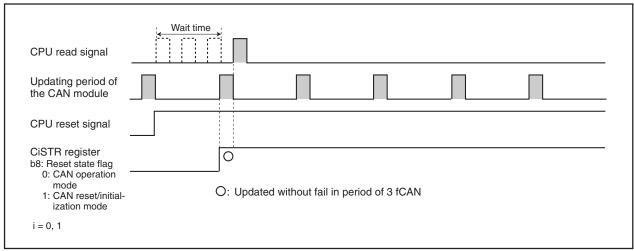

| 23.14.1 Reading CiSTR Register                                                             | 362 |

| 23.14.2 Performing CAN Configuration                                                       | 364 |

| 23.14.3 Suggestions to Reduce Power Consumption                                            | 365 |

| 23.14.4 CAN Transceiver in Boot Mode                                                       | 366 |

| 23.15 Programmable I/O Ports                                                               | 367 |

| 23.16 Dedicated Input Pin                                                                  | 368 |

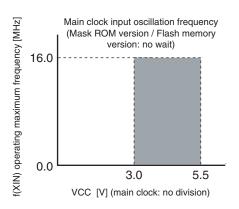

| 23.17 Electrical Characteristic Differences between Mask ROM and Flash Memory Version MCUs | 369 |

| 23.18 Mask ROM Version (Normal-ver. only)                                                  | 370 |

| 23.19 Flash Memory Version                                                                 | 371 |

| 23.19.1 Functions to Prevent Flash Memory from Rewriting                                   | 371 |

| 23.19.2 Stop Mode                                                                          | 371 |

| 23.19.3 Wait Mode                                                                          | 371 |

| 23.19.4 Low Power Dissipation Mode and On-Chip Oscillator Low Power Dissipation Mode       | 371 |

| 23.19.5 Writing Command and Data                                                           | 371 |

| 23.19.6 Program Command                                                                    | 371 |

| 23.19.7 Lock Bit Program Command                                                           | 371 |

| 23.19.8 Operating Speed                                                                    | 371 |

| 23.19.9 Prohibited Instructions                                                            | 372 |

| 23.19.10 Interrupts                                                                        | 372 |

| 23.19.11 How to Access                                                                     | 372 |

| 23.19.12 Rewriting in User ROM Area                                                        | 372 |

| 23.19.13 DMA Transfer                                                                      | 372 |

| 23.20 Flash Memory Programming Using Boot Program                                          | 373 |

| 23.20.1 Programming Using Serial I/O Mode                                                  | 373 |

| 23.20.2 Programming Using CAN I/O Mode                                                     | 373 |

| 23.21 Noise                                                                                | 374 |

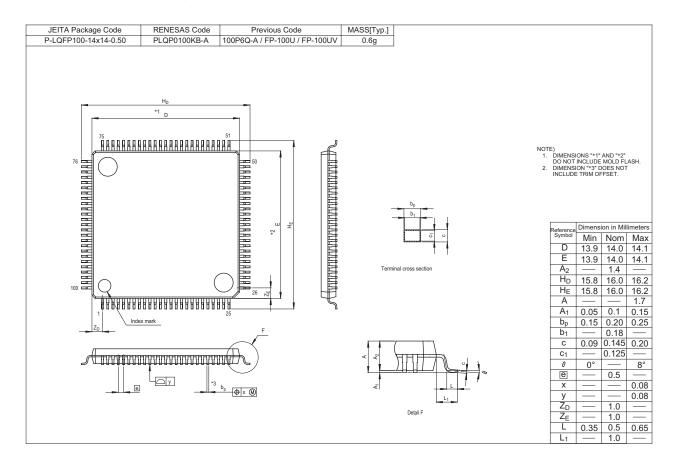

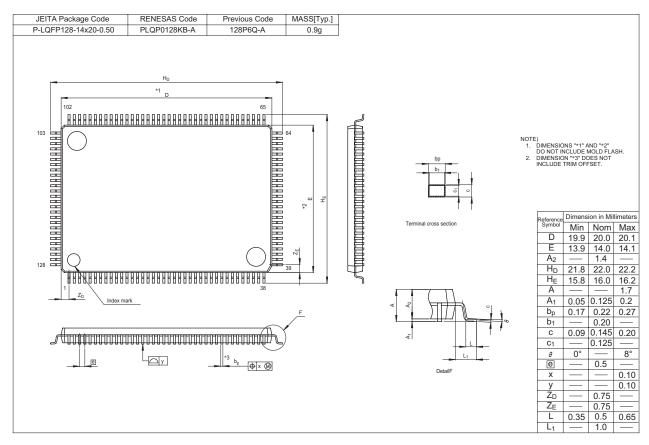

| Appendix 1. Package Dimensions                                                             | 375 |

| Pagistar Inday                                                                             | 277 |

Specifications written in this manual are believed to be accurate, but are not guaranteed to be entirely free of error. Specifications in this manual may be changed for functional or performance improvements. Please make sure your manual is the latest edition.

# SFR Page Reference

| 0000h         0001h           0001h         0001h           0002h         0003h           0004h         Processor Mode Register 0         PM0         40           0005h         Processor Mode Register 1         PM1         41           0006h         System Clock Control Register 0         CM0         58           0007h         System Clock Control Register 1         CM1         59           0008h         Chip Select Control Register 2         CSR         46           0009h         Address Match Interrupt Enable Register PRCR         80           000Dh         Oscillation Stop Detection Register PRCR         80           000Dh         Watchdog Timer Start Register WDTS         102           000Fh         Watchdog Timer Control Register WDC         102           0010h         Address Match Interrupt Register 0         RMAD0         100           0011h         Address Match Interrupt Register 1         RMAD1         100           0012h         Address Match Interrupt Register 1         RMAD1         100           0013h         Address Match Interrupt Register 1         RMAD1         100           0015h         Address Match Interrupt Register 2         RMAD1         100           0018h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Address | Register                            | Symbol  | Page  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------|---------|-------|

| 0002h         0003h         Processor Mode Register 0         PM0         40           0005h         Processor Mode Register 1         PM1         41           0006h         System Clock Control Register 0         CM0         58           0007h         System Clock Control Register 1         CM1         59           0008h         Chip Select Control Register 1         CSR         46           0009h         Address Match Interrupt Enable Register PRCR         80           0000h         Oscillation Stop Detection Register         CM2         60           000Dh         Watchdog Timer Start Register         WDC         102           000Fh         Watchdog Timer Control Register         WDC         102           0010h         Ool1h         Address Match Interrupt Register WDC         102           0013h         Ool1h         Address Match Interrupt Register 1         RMAD0         100           0013h         Ool1h         Address Match Interrupt Register 1         RMAD1         100           0015h         Ool1h         Address Match Interrupt Register 1         RMAD1         100           0016h         Ool7h         Address Match Interrupt Register 1         RMAD1         100           0016h         Ool7h <td< td=""><td>-</td><td>Hogistor</td><td>Cynnon</td><td>i ago</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -       | Hogistor                            | Cynnon  | i ago |

| 0003h         Processor Mode Register 0         PM0         40           0005h         Processor Mode Register 1         PM1         41           0006h         System Clock Control Register 0         CM0         58           0007h         System Clock Control Register 1         CM1         59           0008h         Chip Select Control Register 1         CM1         59           0009h         Address Match Interrupt Enable Register AIER         100           0000h         O00Ch         Oscillation Stop Detection Register         CM2         60           000Dh         O00Eh         Watchdog Timer Start Register         WDC         102           000Fh         Watchdog Timer Start Register         WDC         102           0010h         Watchdog Timer Start Register         WDC         102           0011h         Address Match Interrupt Register 0         RMAD0         100           0013h         Address Match Interrupt Register 1         RMAD1         100           0014h         Address Match Interrupt Register 1         RMAD1         100           0015h         Address Match Interrupt Register 1         RMAD1         100           0016h         O015h         CSE         52           0016h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                                     |         |       |

| 0004h         Processor Mode Register 0         PM0         40           0005h         Processor Mode Register 1         PM1         41           0007h         System Clock Control Register 0         CM0         58           0007h         System Clock Control Register 1         CM1         59           0008h         Chip Select Control Register         CSR         46           0009h         Address Match Interrupt Enable Register         AIER         100           000Dh         Protect Register         CM2         60           000Dh         Oscillation Stop Detection Register         WDC         102           000Fh         Watchdog Timer Start Register         WDC         102           000Fh         Watchdog Timer Control Register         WDC         102           0010h         Watchdog Timer Control Register         WDC         102           0011h         Address Match Interrupt Register 0         RMAD0         100           0014h         A011h         Address Match Interrupt Register 1         RMAD1         100           0017h         Address Match Interrupt Register 2         CSE         52           0016h         Chip Select Expansion Control Register         CSE         52           0017h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0002h   |                                     |         |       |

| 0005h         Processor Mode Register 1         PM1         41           0006h         System Clock Control Register 0         CM0         58           0008h         System Clock Control Register 1         CM1         59           0008h         Chip Select Control Register         CSR         46           0009h         Address Match Interrupt Enable Register         AIER         100           000Bh         Protect Register         PRCR         80           000Dh         Oscillation Stop Detection Register         CM2         60           000Dh         Watchdog Timer Start Register         WDC         102           000Fh         Watchdog Timer Control Register         WDC         102           0010h         Address Match Interrupt Register         WDC         102           0011h         Address Match Interrupt Register 0         RMAD0         100           0015h         Address Match Interrupt Register 1         RMAD1         100           0015h         Address Match Interrupt Register 1         RMAD1         100           0015h         Address Match Interrupt Register 2         RMAD1         100           0015h         Chip Select Expansion Control Register         CSE         52           0015h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0003h   |                                     |         |       |

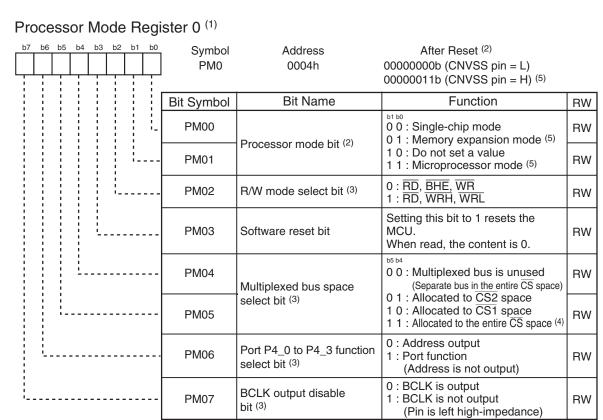

| 0006h         System Clock Control Register 0         CM0         58           0007h         System Clock Control Register 1         CM1         59           0009h         Chip Select Control Register         CSR         46           0009h         Address Match Interrupt Enable Register         AIER         100           000Bh         Protect Register         PRCR         80           000Dh         Oo0Ch         Oscillation Stop Detection Register         CM2         60           000Dh         Watchdog Timer Start Register         WDC         102           0010h         Watchdog Timer Start Register         WDC         102           0010h         Address Match Interrupt Register 0         RMAD0         100           0013h         Address Match Interrupt Register 1         RMAD1         100           0013h         Bollah         Bollah         100           0014h         Bollah         CSE         52           0015h         Chip Select Expans                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0004h   | Processor Mode Register 0           | PM0     | 40    |

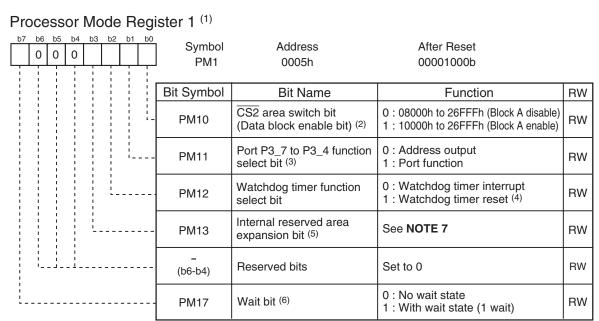

| 0007h         System Clock Control Register 1         CM1         59           0008h         Chip Select Control Register         CSR         46           0009h         Address Match Interrupt Enable Register         AIER         100           0000h         Protect Register         PRCR         80           0000h         Oscillation Stop Detection Register         CM2         60           000Dh         Watchdog Timer Start Register         WDC         102           0010h         Watchdog Timer Control Register         WDC         102           0011h         Address Match Interrupt Register 0         RMAD0         100           0011h         Address Match Interrupt Register 1         RMAD1         100           0014h         0013h         100         100           0014h         0016h         100         100           0017h         100         100         100           0018h         100         100         100           0019h         100         100         100           0019h         100         100         100           0019h         100         100         100           0019h         100         100         100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0005h   | Processor Mode Register 1           | PM1     | 41    |

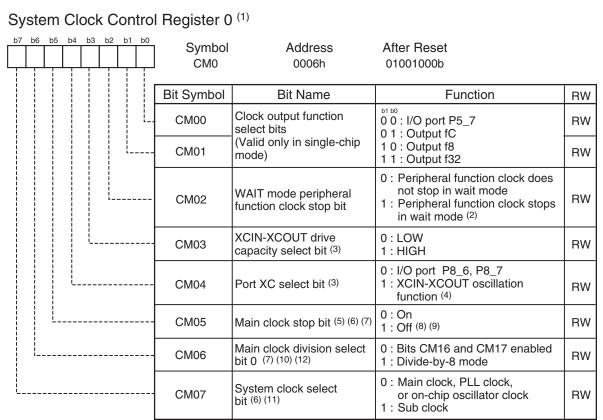

| 0008h         Chip Select Control Register         CSR         46           0009h         Address Match Interrupt Enable Register         AIER         100           000Bh         Protect Register         PRCR         80           000Dh         Oscillation Stop Detection Register         CM2         60           000Eh         Watchdog Timer Start Register         WDC         102           0010h         Odorba         Watchdog Timer Control Register         WDC         102           0010h         Address Match Interrupt Register         WDC         102           0012h         Address Match Interrupt Register I         RMAD0         100           0012h         Address Match Interrupt Register I         RMAD1         100           0012h         Address Match Interrupt Register I         RMAD1         100           0013h         Address Match Interrupt Register I         RMAD1         100           0014h         Address Match Interrupt Register I         RMAD1         100           0015h         Address Match Interrupt Register I         RMAD1         100           0014h         Address Match Interrupt Register I         RMAD1         100           0015h         CSE         52         52         52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0006h   | System Clock Control Register 0     | CM0     | 58    |

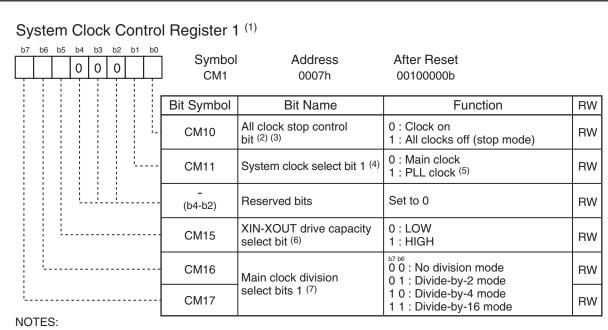

| 0009h         Address Match Interrupt Enable Register         AIER         100           000Ah         Protect Register         PRCR         80           000Ch         Oscillation Stop Detection Register         CM2         60           000Dh         Watchdog Timer Start Register         WDC         102           000Fh         Watchdog Timer Control Register         WDC         102           0010h         O010h         Address Match Interrupt Register 0         RMAD0         100           0013h         Address Match Interrupt Register 1         RMAD1         100           0014h         Address Match Interrupt Register 1         RMAD1         100           0015h         Address Match Interrupt Register 1         RMAD1         100           0014h         Chip Select Expansion Control Register 2         CSE         52           0015h         Chip Select Expansion Control Register 2         PM2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0007h   | System Clock Control Register 1     | CM1     | 59    |

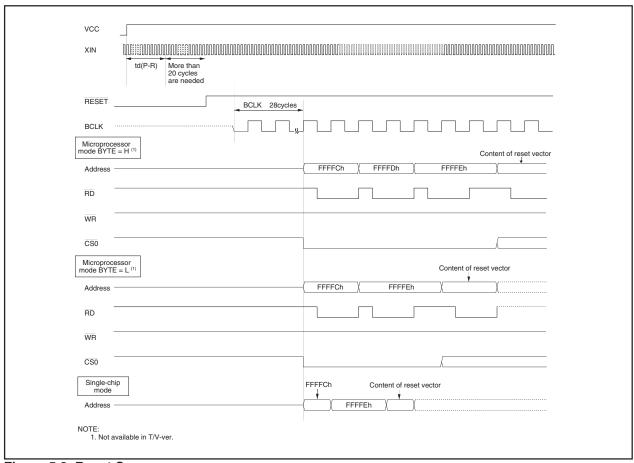

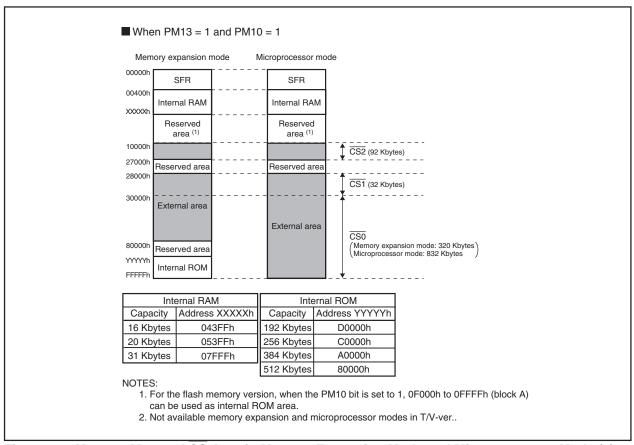

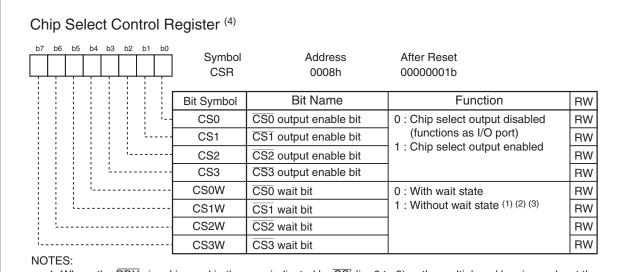

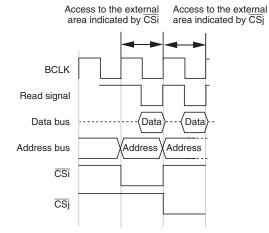

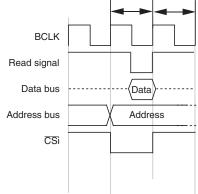

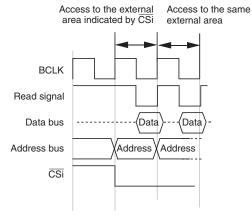

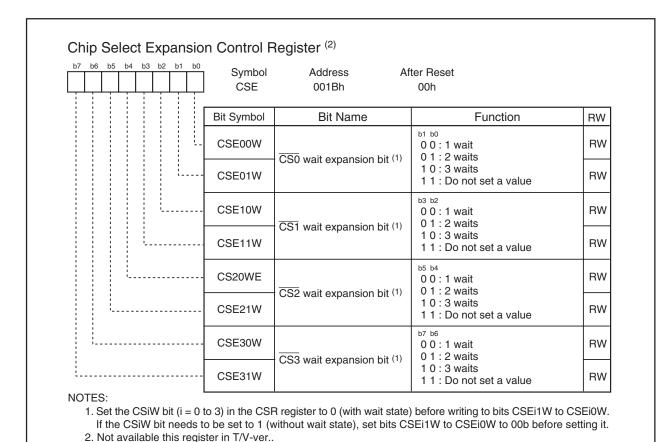

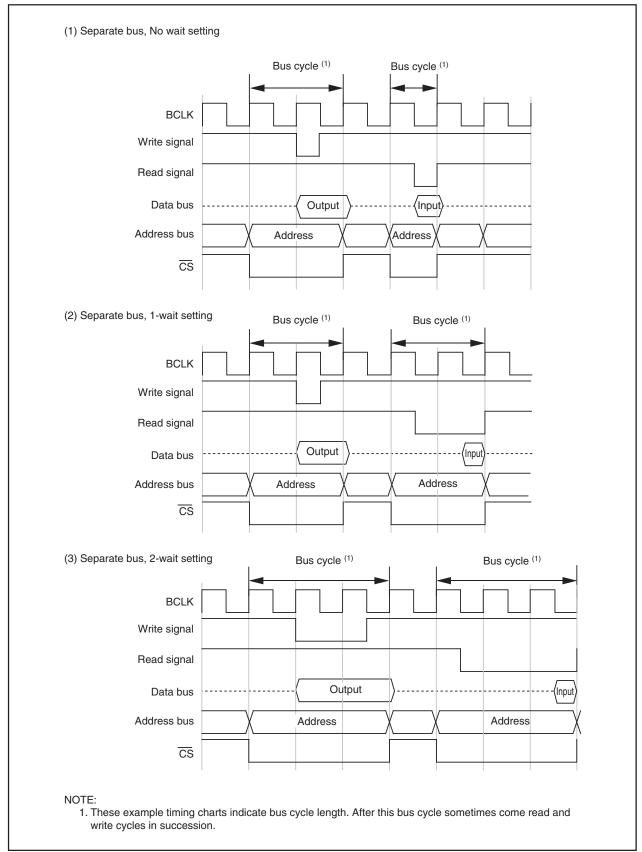

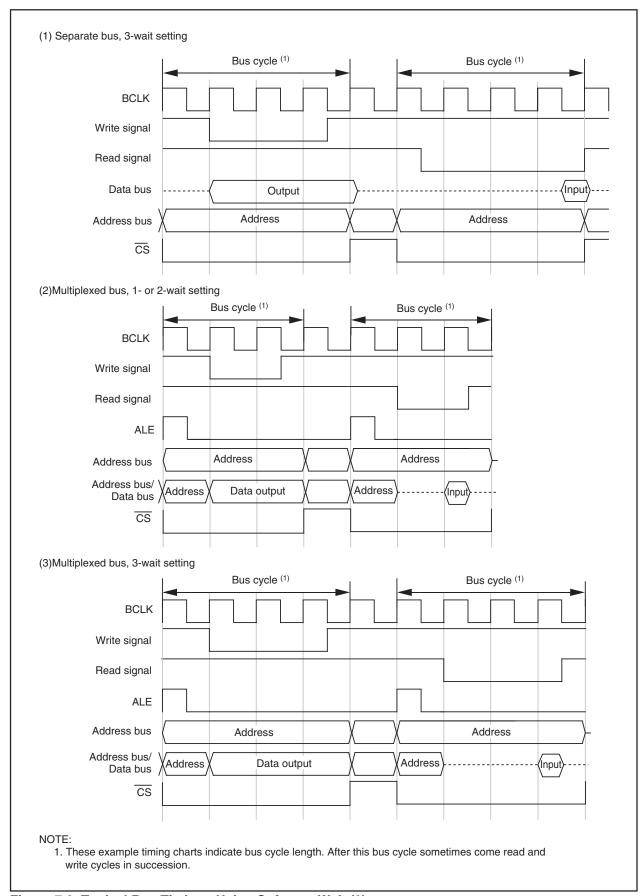

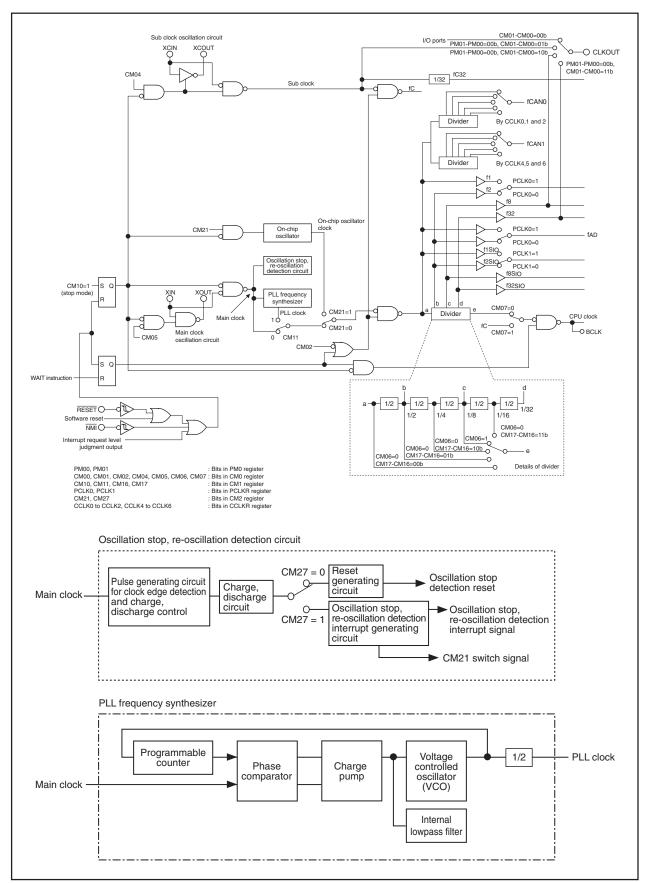

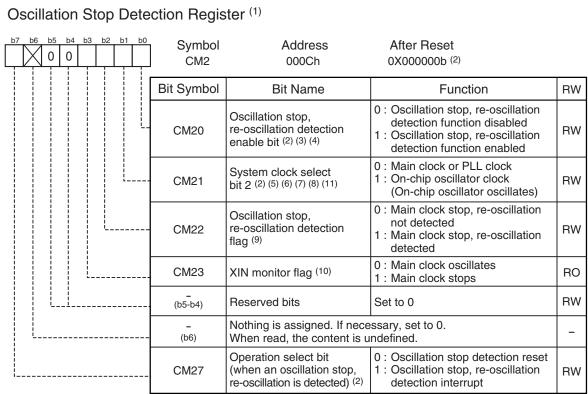

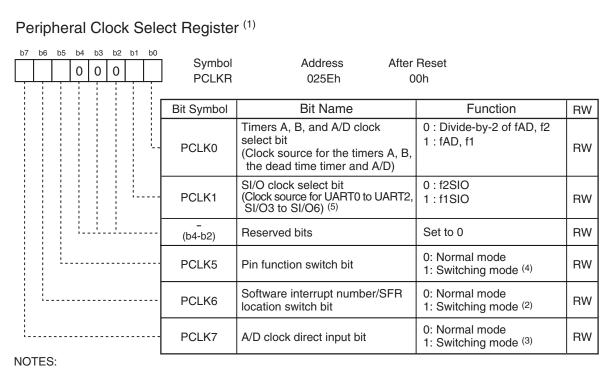

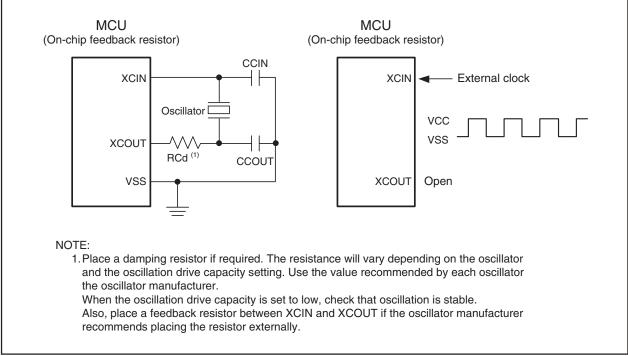

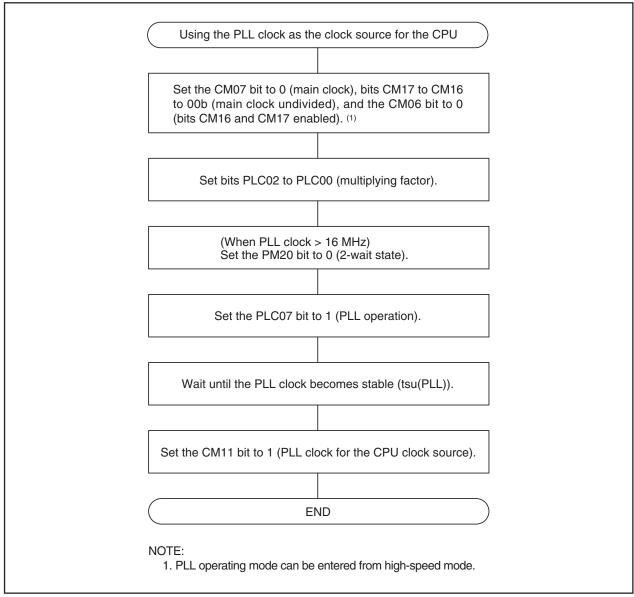

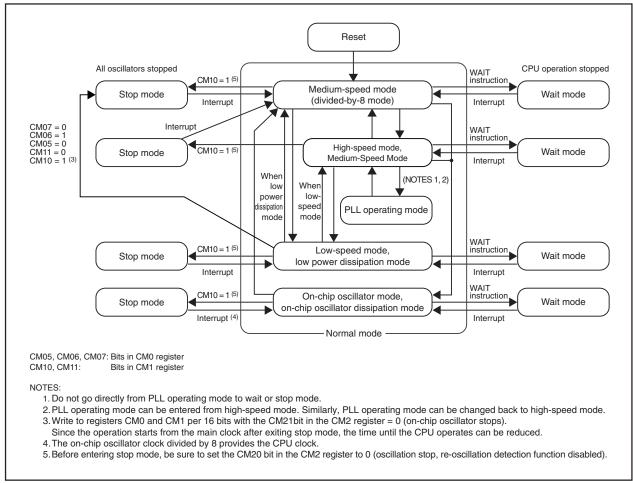

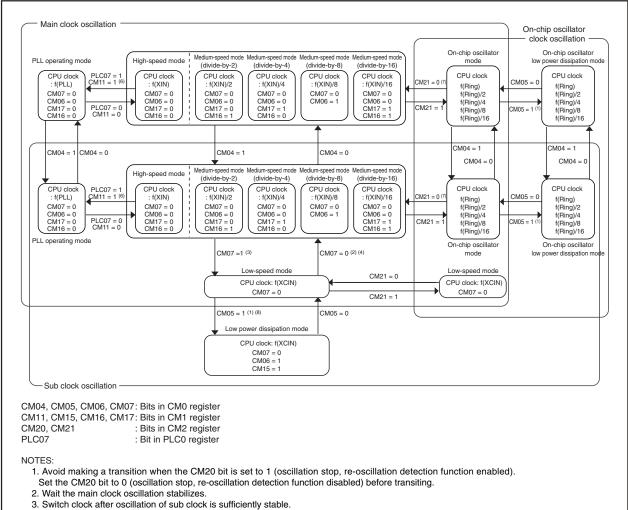

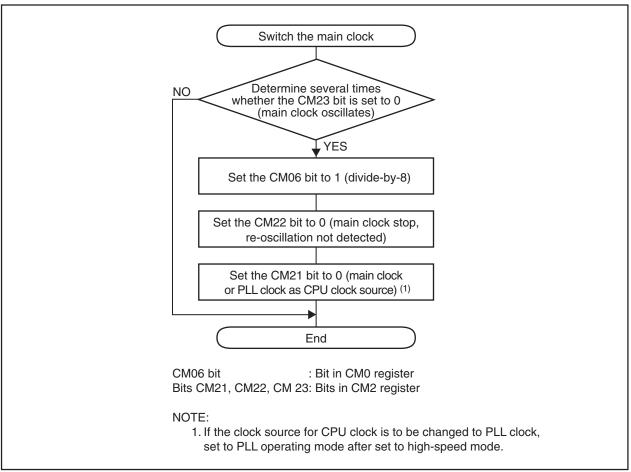

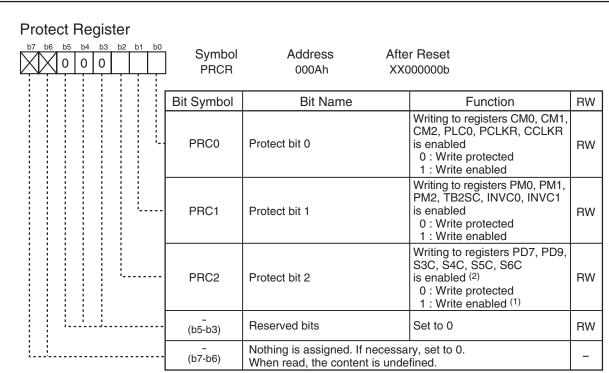

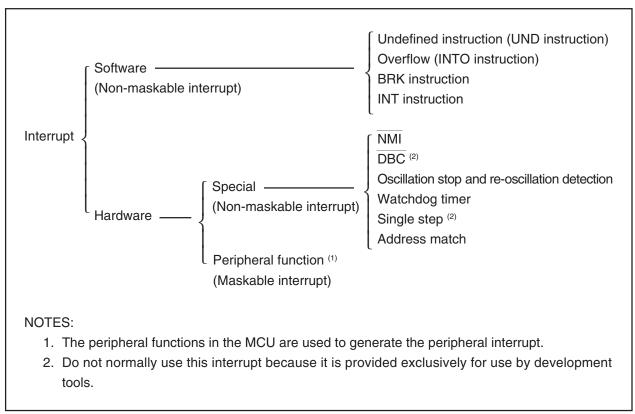

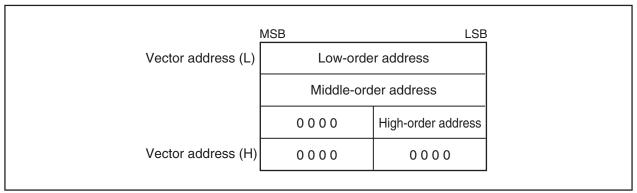

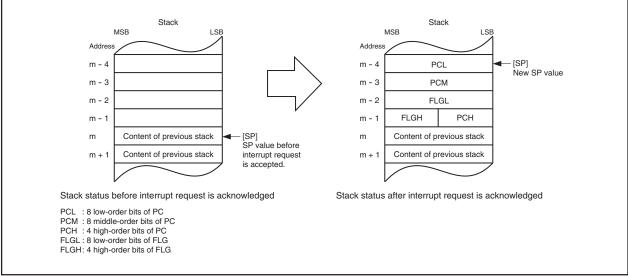

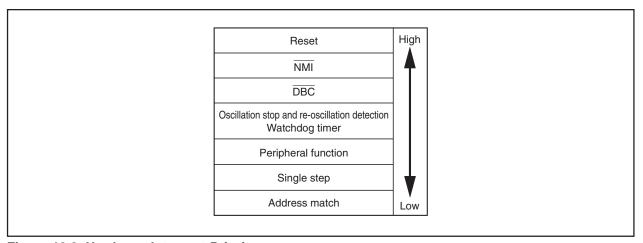

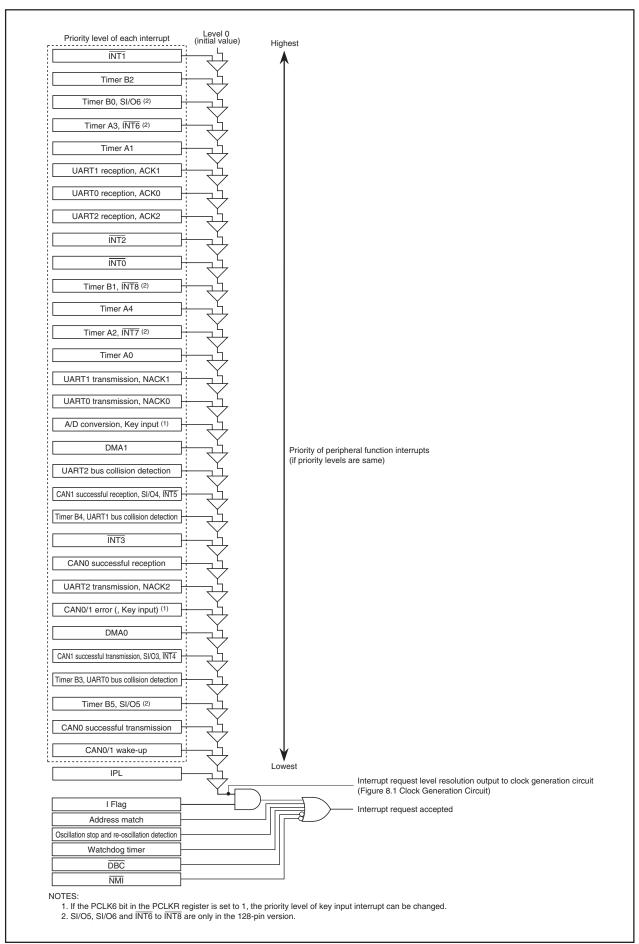

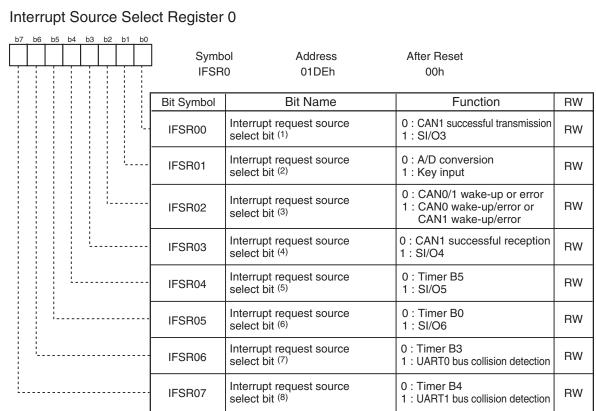

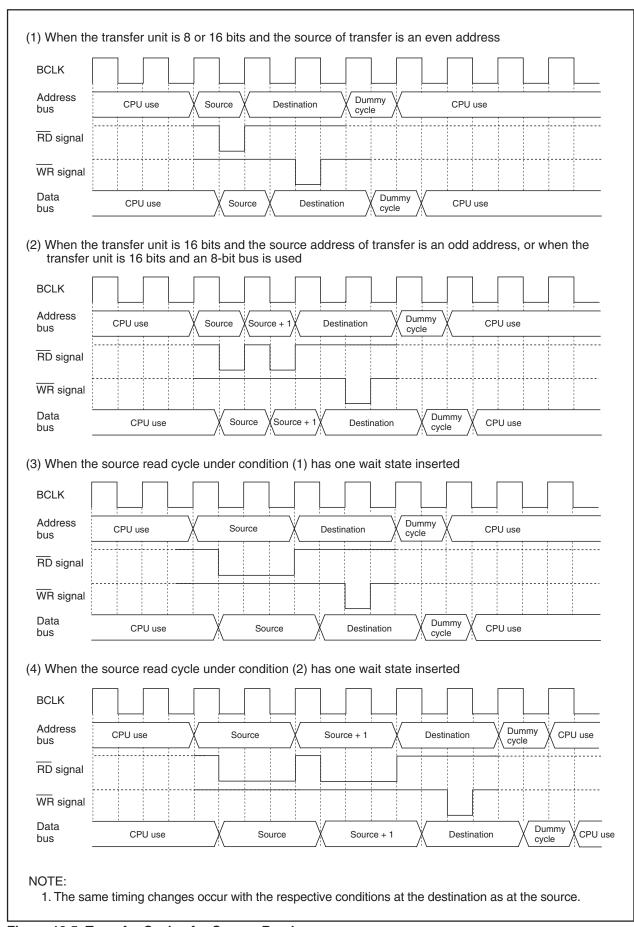

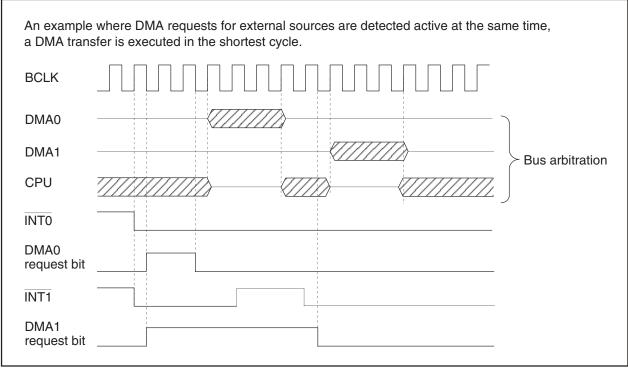

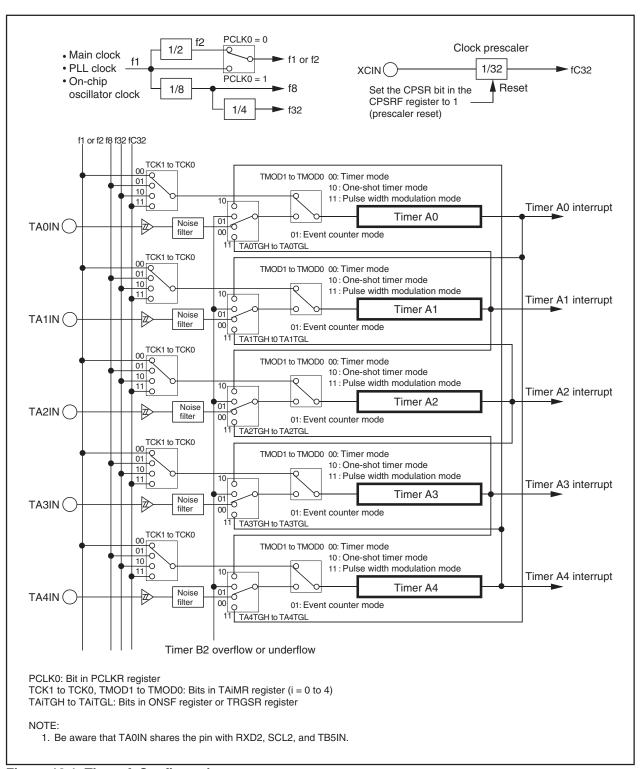

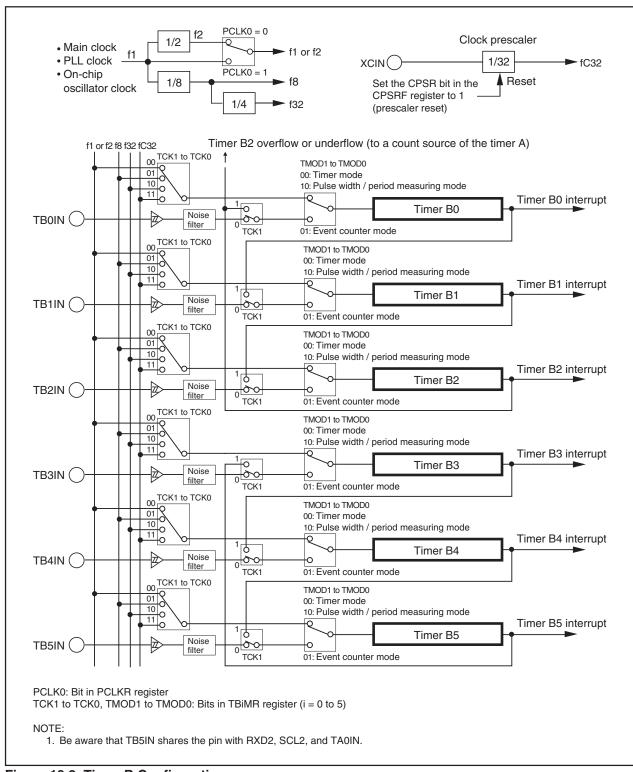

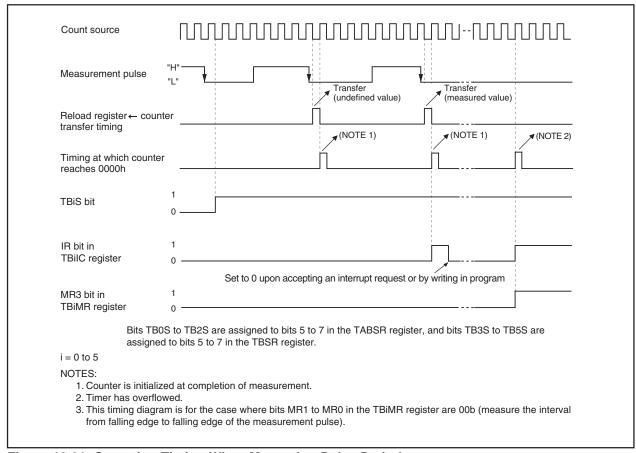

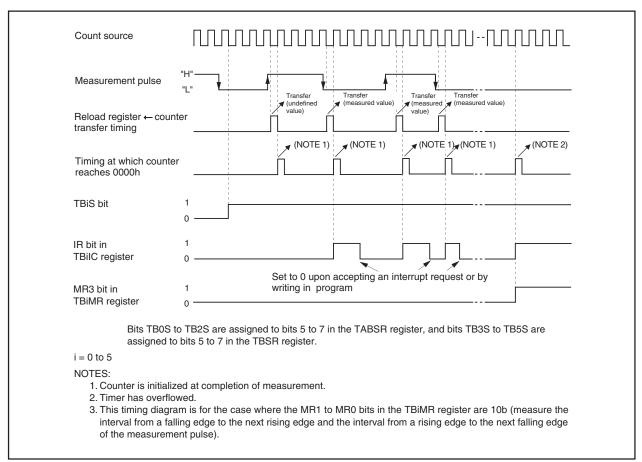

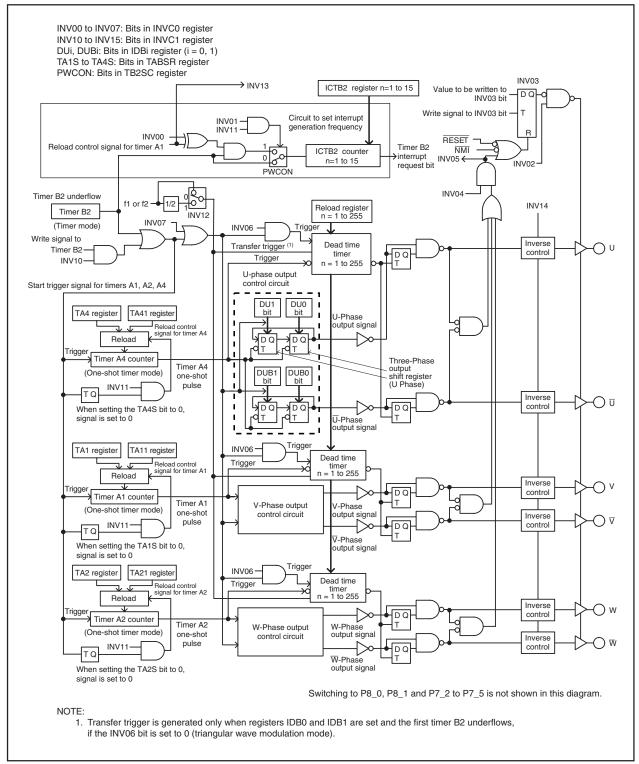

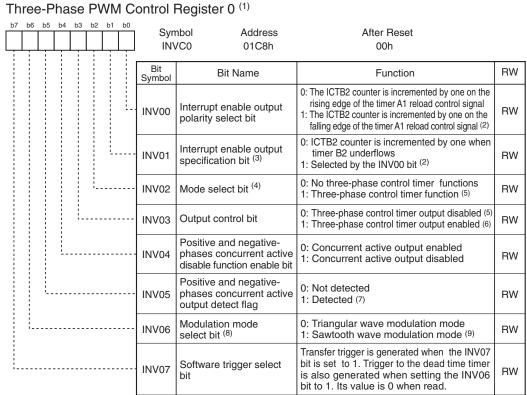

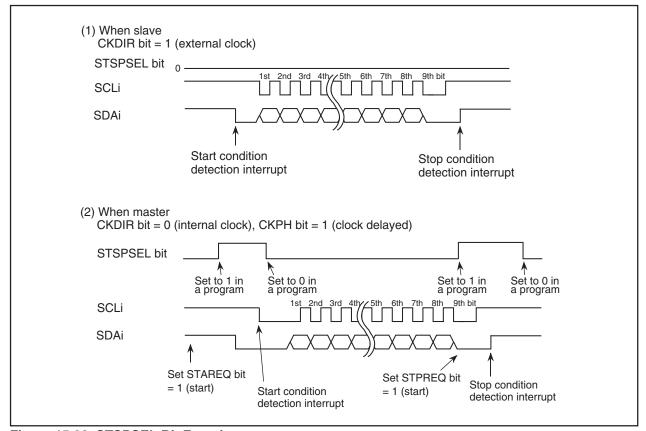

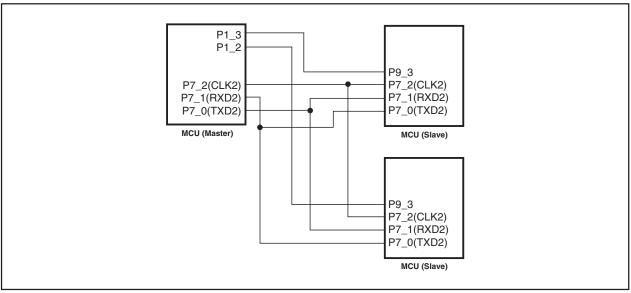

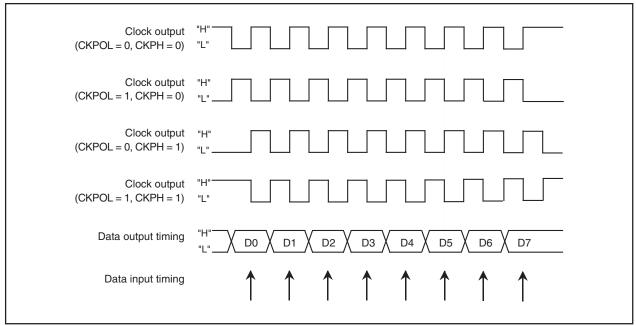

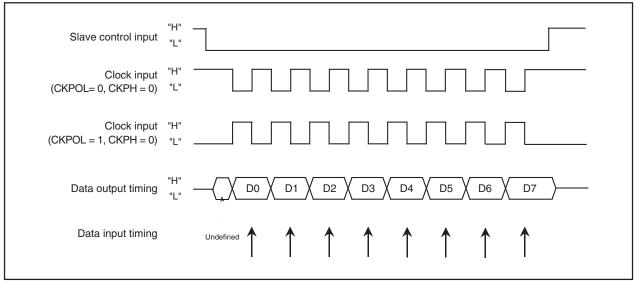

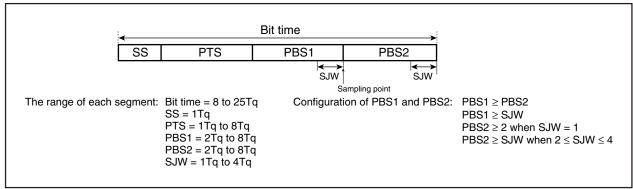

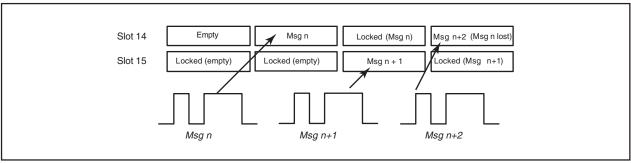

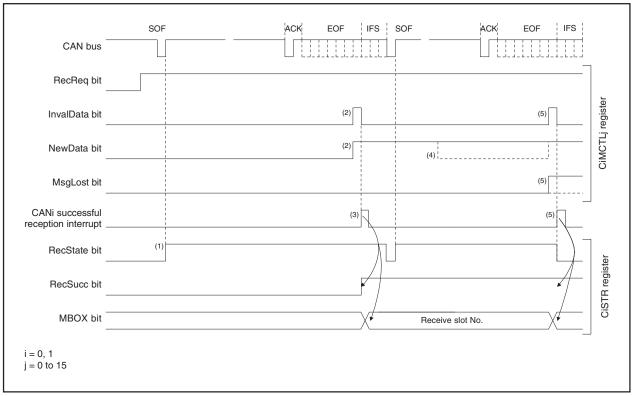

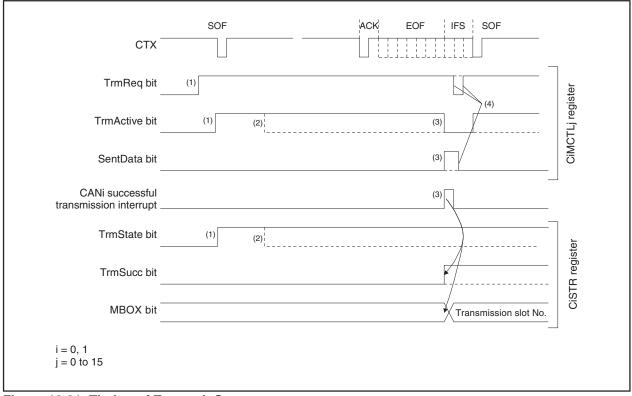

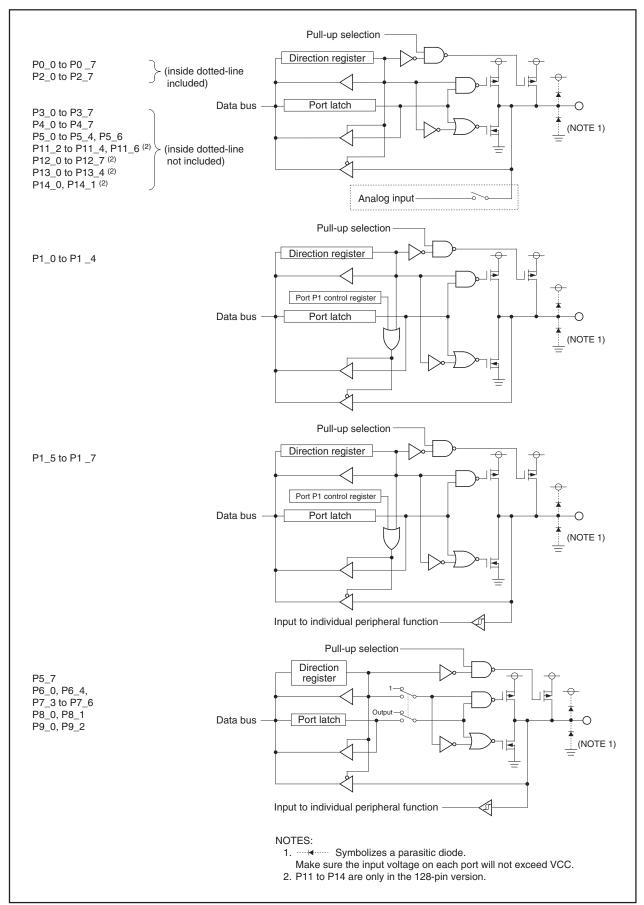

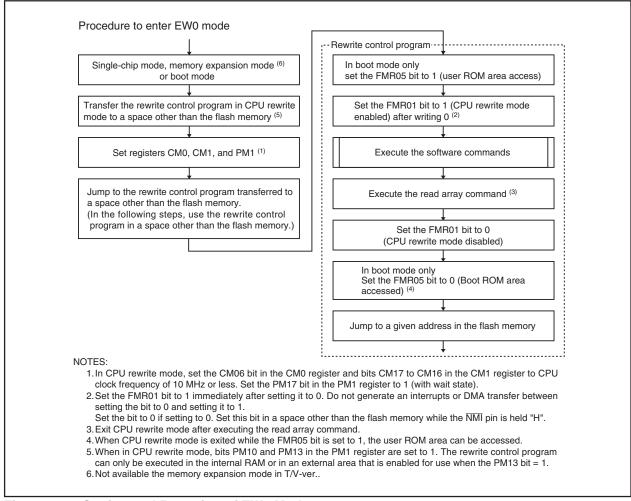

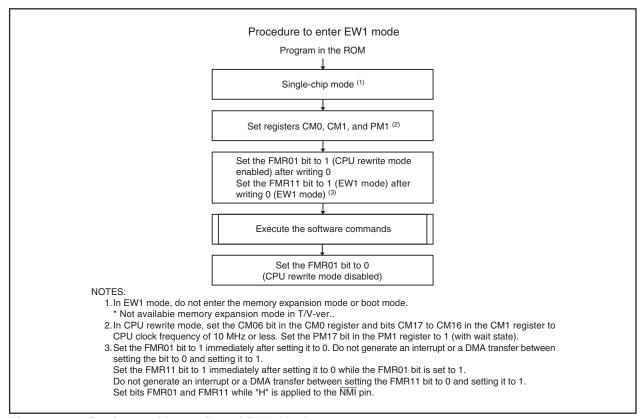

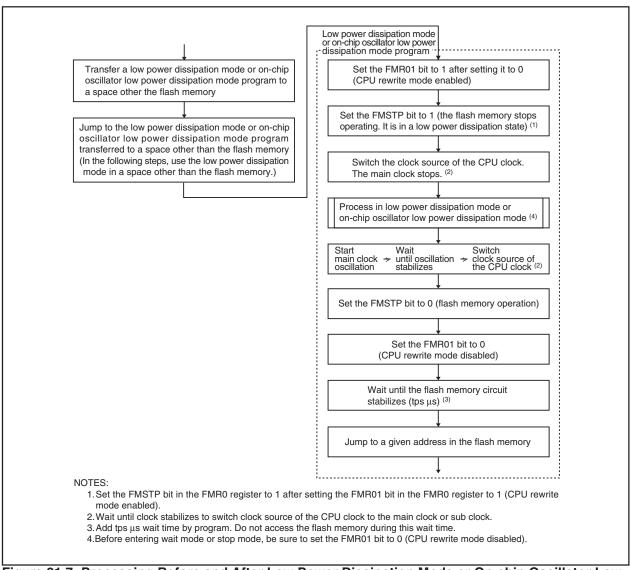

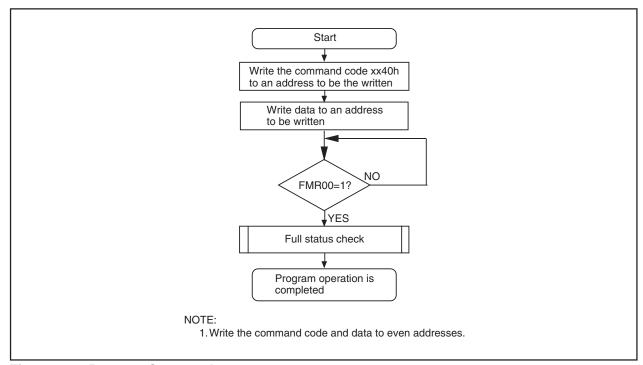

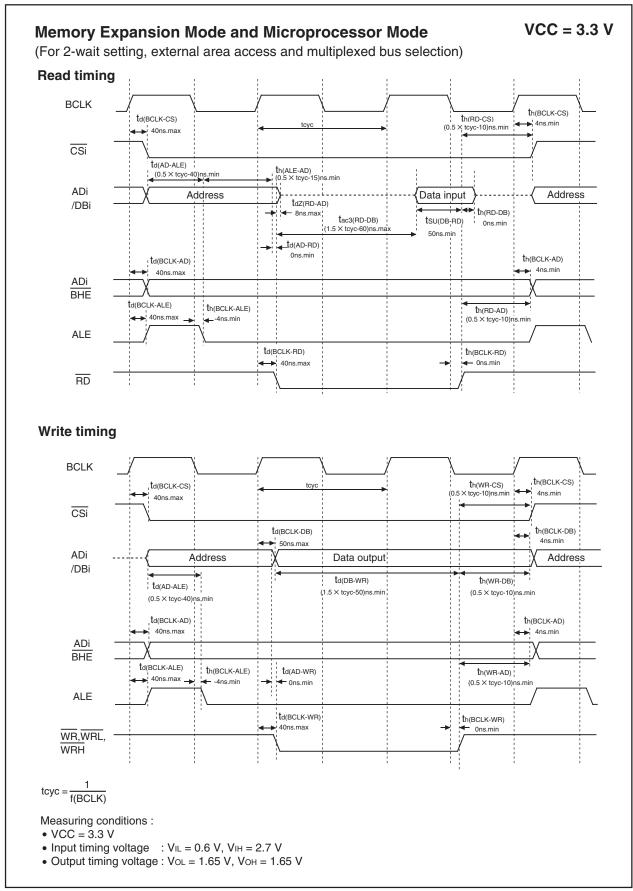

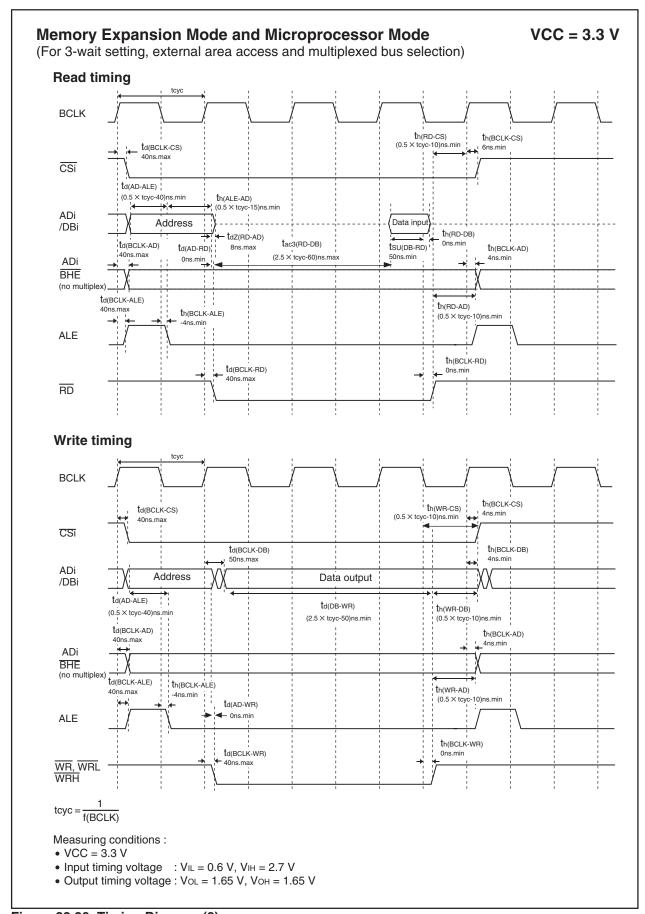

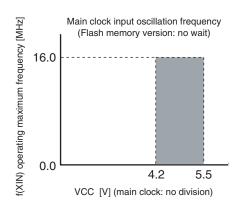

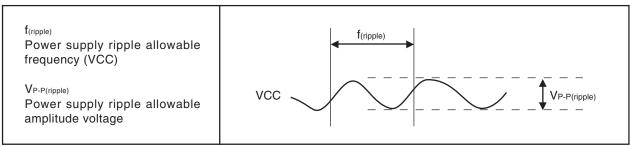

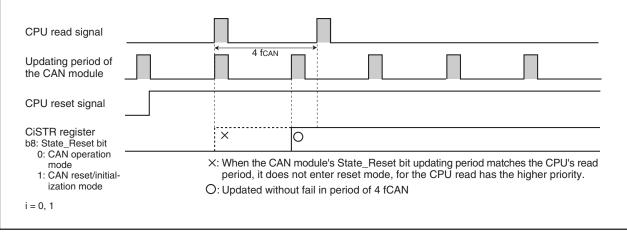

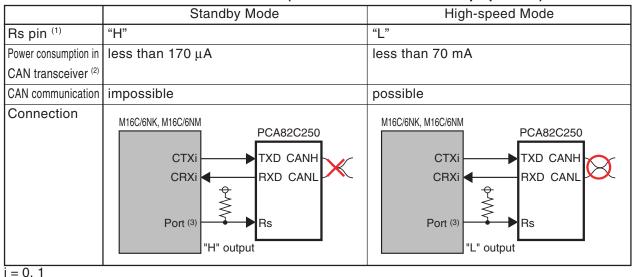

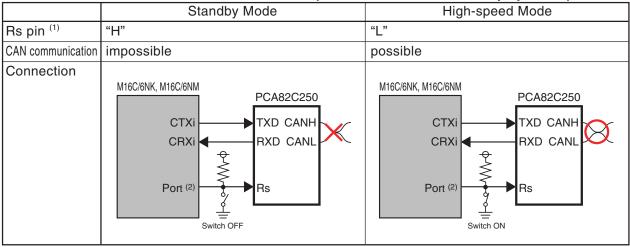

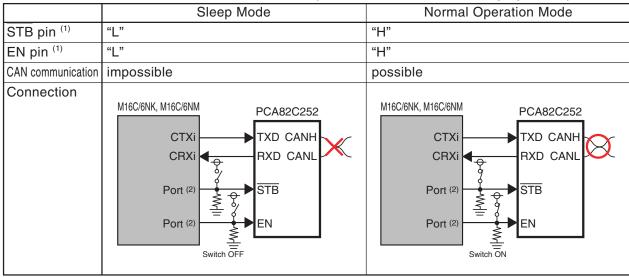

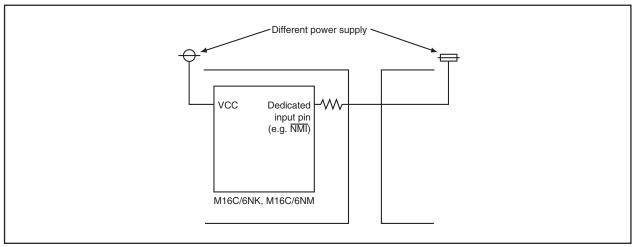

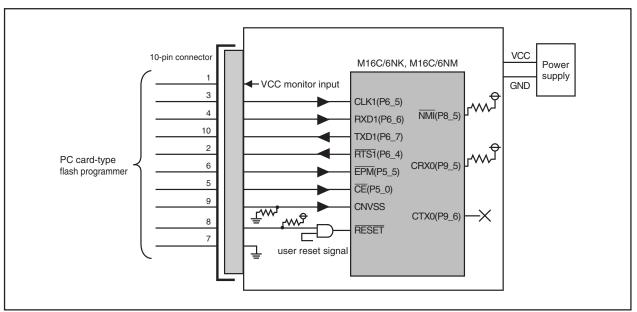

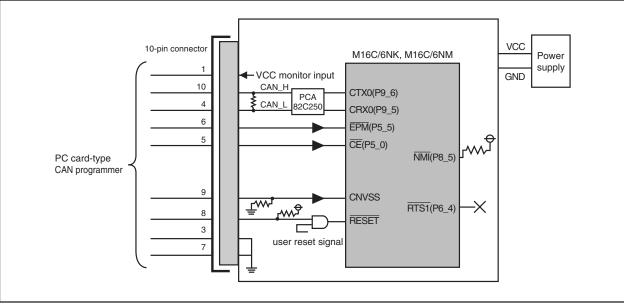

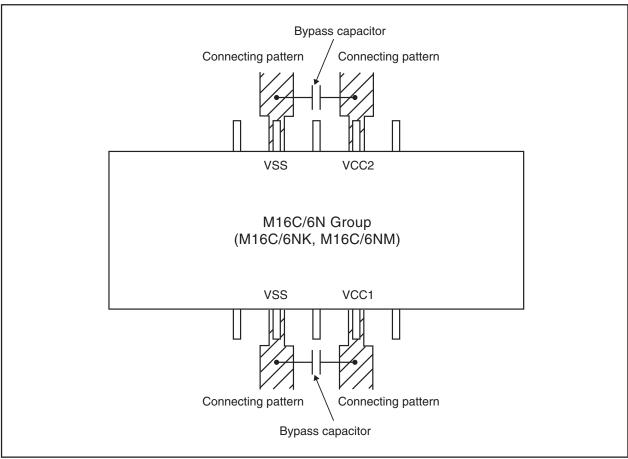

| O00Ah                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0008h   | Chip Select Control Register        | CSR     | 46    |