# Errata Sheet and Guidelines for MAX 10 ES Devices

# **Contents**

| Device Errata for MAX 10 ES Devices                   | 1-1 |

|-------------------------------------------------------|-----|

| ADC Prescalar                                         | 1-1 |

| ESD Performance                                       | 1-2 |

| Timing Model Adjustment                               | 1-2 |

| Device Guidelines for MAX 10 ES Devices               | 2-1 |

| Recommended Power-up Sequencing for MAX 10 ES Devices | 2-1 |

| Full Chip Erase Prior to Initial Device Programming   |     |

| Migration Guidelines                                  |     |

| Document Revision History                             | 3-1 |

## **Device Errata for MAX 10 ES Devices**

1

2015.06.12

ES-1040

This errata sheet provides information about known device issues affecting MAX<sup>®</sup> 10 engineering sample (ES) devices.

Note: • ES devices are not intended to be used for volume production or device qualification testing.

• ES devices are intended to be used at nominal voltage and nominal temperature only for DDR3 external memory interface (EMIF) support.

Table 1-1: Device Errata for MAX 10 ES Devices

This table lists the specific device issues and the affected MAX 10 ES devices.

| Issue                                                                                                             | Affected Devices | Planned Fix                                                  |

|-------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------|

| ADC Prescalar on page 1-1                                                                                         | 10M08 ES         | Production Devices                                           |

| <ul><li>ADC prescalar gain error</li><li>ADC prescalar THD performance</li></ul>                                  |                  |                                                              |

| ESD Performance on page 1-2  HBM ESD performance for MAX 10  ES devices is below target level                     | 10M08 ES         | Production Devices                                           |

| Timing Model Adjustment on page 1-2  Timing model adjustment on I/O-to-Core and Core-to-I/O for MAX 10 ES devices | 10M08 ES         | Updated Timing Model in the Quartus II software version 15.0 |

## **ADC Prescalar**

The ADC prescalar in the 10M08 ES devices does not meet datasheet specifications, affecting gain error and total harmonic distortion (THD) specifications. Other specifications related to prescalar are not affected. This issue will be fixed in production devices.

© 2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at <a href="https://www.altera.com/common/legal.html">www.altera.com/common/legal.html</a>. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008 Registered

#### Table 1-2: Gain Error and Drift Specifications for 10M08 ES Devices

| Parameter                  | Symbol            | Condition         | Channel | Min | Тур | Max | Unit |

|----------------------------|-------------------|-------------------|---------|-----|-----|-----|------|

| Gain array and drift       | luist Eccin       | With prescalar on | 8       | 2   | _   | 5   | %FS  |

| Gain error and drift Egain | With prescalar on | 16                | -1      | _   | 1   | %FS |      |

#### Table 1-3: Total Harmonic Distortion Specifications for 10M08 ES Devices

| Parameter                    | Symbol | Condition                                                                      | Min | Тур | Max | Unit |

|------------------------------|--------|--------------------------------------------------------------------------------|-----|-----|-----|------|

| Total Harmonic<br>Distortion | THD    | F <sub>IN</sub> = 50 kHz, F <sub>S</sub> = 1<br>MHz, PLL, Prescalar<br>enabled | 61  | _   | _   | dB   |

### **ESD Performance**

HBM ESD performance for 10M08 ES devices is below target levels (CDM meets targets). Altera will improve ESD performance in production devices.

As per JEDEC document JESD625b, follow the standard ESD handling guidelines, particularly for human handling, (i.e. wear proper ground strap) when handling 10M08 ES devices.

## **Timing Model Adjustment**

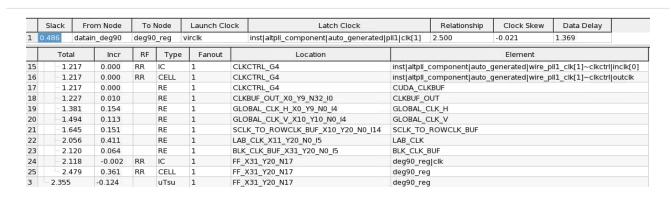

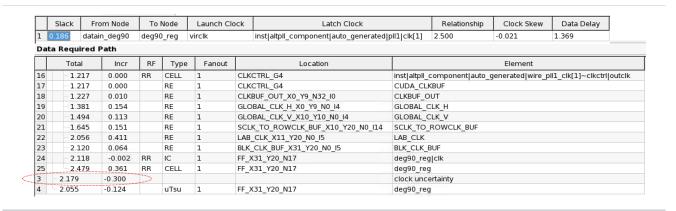

To better align the Quartus<sup>®</sup> II timing models with silicon characterization, Altera recommends adjusting the timing for I/O-to-Core and Core-to-I/O data transfer in MAX 10 ES devices. For temporary solution, add 300 ps (0.3 ns) clock uncertainty in TimeQuest Timing Analyzer.

To add 300 ps (0.3 ns) clock uncertainty in TimeQuest Timing Analyzer, add the following constraints in the Synopsys Design Constraints File (.sdc):

- set\_clock\_uncertainty -setup -to <clock name> -setup -add 0.3

- set\_clock\_uncertainty -hold -enable\_same\_physical\_edge -to <clock name> -add 0.3

#### For example:

```

set_clock_uncertainty -to { inst|altpll_component|auto_generated|pll1|

clk[1] } -setup 0.3

```

After adding the .sdc file constraint, a clock uncertainty row is added in Data Required Path in the timing report.

Device Errata for MAX 10 ES Devices

#### Figure 1-1: Timing Report Before 300 ps Clock Uncertainty is Added

Figure 1-2: Timing Report After 300 ps Clock Uncertainty is Added

## **Device Guidelines for MAX 10 ES Devices**

2

2015.06.12

ES-1040

This guidelines sheet provides Altera's recommended guidelines when using MAX 10 ES devices.

- **Note:** ES devices are not intended to be used for volume production or device qualification testing.

- ES devices are intended to be used at nominal voltage and nominal temperature only for DDR3 EMIF support.

## Recommended Power-up Sequencing for MAX 10 ES Devices

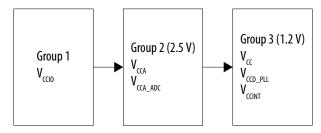

To ensure the minimum current draw during power up and configuration for MAX 10 dual supply ES devices, follow the recommended power-up sequence as shown in the figure below.

#### Figure 2-1: Recommended Power-up Sequence

The power rails in each group must be ramped up to a minimum of 90% of their full rail before the next group starts.

## **Full Chip Erase Prior to Initial Device Programming**

You must perform a full chip erase prior to device programming when you use the MAX 10 device for the first time. The full chip erase prevents the reconfiguration watchdog timer from timing out. The full chip erase must be done only prior to initial programming.

© 2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at <a href="https://www.altera.com/common/legal.html">www.altera.com/common/legal.html</a>. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008 Registered

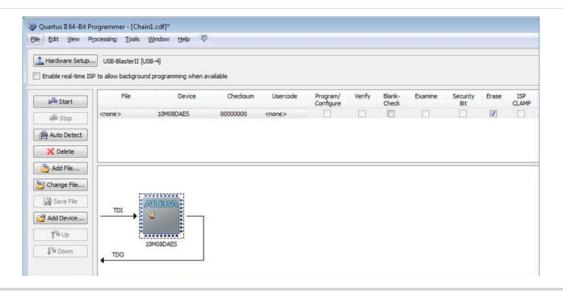

For full chip erase, follow these steps:

- 1. Open the Quartus II Programmer.

- 2. In the **Programmer** window, click **Hardware Setup** and select **USB Blaster**.

- 3. Click Auto Detect on the left pane.

- **4.** Select the device and set the **Erase** column as shown in the following figure.

- **5.** Click **Start** to start full chip erase.

Figure 2-2: The Quartus II Programmer

## **Migration Guidelines**

This migration guidelines is applicable if you plan to use MAX 10 SC or SF variant (for single supply devices) and DC or DF variant (for dual supply devices) in production devices.

Altera recommends designing your board with MAX 10 ES device SA or DA variant according to the recommendation for SC or SF variant (for single supply devices) and DC or DF variant (for dual supply devices). There are cross variants pin mismatches between MAX 10 ES devices and MAX 10 production devices. You can migrate the pins as recommended in the following tables without impact to your design.

Table 2-1: MAX 10 Devices Migration from ES Device SA Variant to Production Device SC or SF Variant

| MAX 10 ES Device SA Variant Pin | MAX 10 Production Device SC or SF Variant Pin |

|---------------------------------|-----------------------------------------------|

| ADC_VREF                        | VCCA                                          |

| ANAIN1                          | GND                                           |

| REFGND                          | GND                                           |

| ADC1IN[18]                      | 1/0                                           |

Table 2-2: MAX 10 Devices Migration from ES Device DA Variant to Production Device DC or DF Variant

| MAX 10 ES Device DA Variant Pin | MAX 10 Production Device DC or DF Variant Pin |

|---------------------------------|-----------------------------------------------|

| ADC_VREF                        | VCCA                                          |

| ANAIN[12]                       | GND                                           |

| REFGND                          | GND                                           |

| ADC1IN[116] or ADC[12]IN[18]    | 1/0                                           |

| VCCA_ADC                        | VCCA                                          |

| VCCINT                          | VCC                                           |

## **Document Revision History**

3

2015.06.12

ES-1040

Subscribe 🖵

Send Feedback

| Date           | Version    | Changes                                                                                                                                                                                                                                                             |

|----------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2015      | 2015.06.12 | Updated the note in Device Errata and Device Guidelines chapters: ES devices are not intended to be used for volume production or device qualification testing.                                                                                                     |

| March 2015     | 2015.03.06 | <ul> <li>Added EMIF guideline: ES devices are intended to be used at nominal voltage and nominal temperature only for DDR3 external memory interface (EMIF) support.</li> <li>Removed transient current guidelines.</li> <li>Added Migration Guidelines.</li> </ul> |

| November 2014  | 2014.11.11 | <ul> <li>Added total harmonic distortion specifications for 10M08 ES devices in ADC Prescalar errata.</li> <li>Added errata for timing model adjustment.</li> </ul>                                                                                                 |

| September 2014 | 2014.09.22 | Initial release.                                                                                                                                                                                                                                                    |

© 2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at <a href="https://www.altera.com/common/legal.html">www.altera.com/common/legal.html</a>. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008 Registered