Informações

DAC explora o papel da IA e do ML nos mercados

Moscone Center, San Francisco, vai sediar DAC 25-28 junho

Soluções OneSpin e Austemper Design Systems Ambos destacarão ferramentas para a verificação de segurança funcional. O Austemper se concentrará no desenvolvimento de sistemas de missão crítica, com o pacote de ferramentas KaleidoScope que suporta design analógico para propagação simultânea de falhas de sinal misto. O conjunto de ferramentas automatizadas possui recursos de análise, síntese e verificação de segurança para aplicativos orientados a certificação. É usado para projetos automotivos de larga escala em ADAS e condução autônoma. A simulação de falhas simultâneas inclui simulações recomendadas pela ISO 26262 para atender aos requisitos da ASIL.

Recentemente, a empresa firmou uma parceria com a OneSpin Solutions para adotar uma metodologia suportada por ferramentas para aplicações de segurança funcional, combinando um fluxo de projeto e verificação, que será demonstrado no estande do OneSpin. Mecanismos de segurança de hardware são inseridos em projetos de chip e as ferramentas OneSpin Solutions verificam formalmente a lógica de segurança do hardware. A verificação de equivalência garante que a lógica de segurança inserida não afeta a funcionalidade regular e a análise de detecção de falhas verifica se os mecanismos de segurança estão funcionando corretamente no caso de erros aleatórios.

O OneSpin também está promovendo seu kit de Qualificação de Ferramentas, após a verificação pela TÜV SÜD de seus processos de desenvolvimento de ferramentas. O kit inicial está disponível para a ferramenta ECDA FPGA EC-FPGA da empresa, uma verificação de equivalência sequencial automática que evita que os fluxos de projeto do FPGA apresentem erros de implementação. O kit é certificado conforme ISO 26262, IEC 61508 e EN 50128.

Insights sobre FPGA

Ainda com design FPGA, Plunificar colaborou com a Xilinx para oferecer o pacote de design Vivado na nuvem, através da plataforma Plunify Cloud. Designers pagam apenas 50c para compilar um projeto Vivado na nuvem da Amazon Web Services (AWS), incluindo licenças.

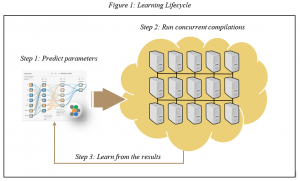

A empresa também demonstrará melhorias em seu software de fechamento de tempo InTime para otimizar o tempo de FPGA na nuvem (Figura 1). A Metodologia de Otimização InTime pode melhorar a frequência do relógio em 20 a 80% e atender aos requisitos de tempo em dias, em vez de semanas, via aprendizado de máquina. O software também acelera o fechamento e otimização de tempo e é acessado via nuvem.

A empresa também demonstrará melhorias em seu software de fechamento de tempo InTime para otimizar o tempo de FPGA na nuvem (Figura 1). A Metodologia de Otimização InTime pode melhorar a frequência do relógio em 20 a 80% e atender aos requisitos de tempo em dias, em vez de semanas, via aprendizado de máquina. O software também acelera o fechamento e otimização de tempo e é acessado via nuvem.

Promovendo a tecnologia eFPGA, Achronix Semiconductor está colaborando com especialista em IP FUNDIDA para aumentar o rendimento e economizar no armazenamento de memória.

Os dois expositores explicarão como o IP de compactação sem perdas da CAST foi transferido para o portfólio FPGA da Achronix para uso em aplicativos de transferência de dados de data center e de borda móvel. A implementação de hardware do padrão de compactação sem perdas para Deflate, GZIP e ZLIB é compatível com implementações de software usadas para compactação ou descompactação para fornecer até 100 Gbit / s com baixa compactação e baixa latência, juntamente com a tecnologia Speedface eFPGA para mover e armazenar grandes dados com baixo consumo de energia.

CAST portou seu IP para FPGAs da Achronix

Eficiência energética

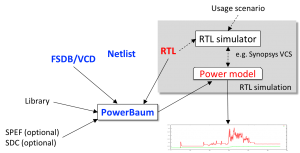

Falando em gerenciamento de energia, outro expositor, Baum, identifica a eficiência energética como a área mais subdesenvolvida no design de chips. Sua ferramenta automatizada de análise e modelagem de energia é projetada para projetos automotivos, IoT, móveis, de rede e de servidor. O PowerBaum 2.0 (Figura 3) suporta energia estática e dinâmica, recebendo descrições de RTL e netlist, e adiciona suporte para análise de energia com emulação de hardware. Isso, diz a empresa, permite que os engenheiros consertem erros de energia em cenários realistas de software. A ferramenta também suporta análises com temperaturas arbitrárias especificadas por projetistas, para avaliar os efeitos da temperatura no consumo de energia de um projeto.

No DAC, a empresa também apresentará o PowerWurzel, um mecanismo de análise de energia de nível de porta a ser integrado ao PowerBaum para modelagem de energia.

Figura 3 As ferramentas da Baum analisam a eficiência energética

Ferramentas de design e verificação de SoC baseadas em nuvem para design de IC Métricas inclua o Cloud Simulator e o Verification Manager, projetados para gerenciar requisitos e recursos de simulação, ajustando-os para cima ou para baixo a cada minuto. A empresa alega que o Google Cloud permite capacidade ilimitada de simulação SystemVerilog compatível com UVM e gerenciamento de verificação nativo baseado na Web para tempos de regressão mais rápidos, erros de código de troncos reduzidos e cobertura de código previsível.

Além de expositores, o evento abriga sessões técnicas e um programa de palestras abordando áreas temáticas. Este ano, por exemplo, a Cadence apresentará um tutorial sobre "Segurança Funcional e Confiabilidade para Aplicativos Automotivos", e um sobre aprendizado de máquina ("Aprendizado de Máquina Leva o Desempenho de Reconhecimento de Fala ao Próximo Nível"). Uma palestra de Anna-Katrina Shedletsky, Instrumental, na segunda-feira, 25 de junho, enfocará "Automação de Inteligência: Aprendizado de Máquina e o Futuro da Fabricação". Usando ML e AI para a robótica socialmente assistida (SAR) é explorado na palestra de quinta-feira por Maja Matarić, da Universidade do Sul da Califórnia, que apresentará "Automação versus Aumento: Robôs Inteligentes e o Futuro do Trabalho".

Outro keynote defende o RISC-V como um meio para liberar arquitetos de arquiteturas proprietárias de conjuntos de instruções (ISAs). David A Patterson, do Google e da Universidade da Califórnia, apresentará "A New Golden Age for Computer Architecture: Aceleradores Específicos de Domínio e Open RISC-V".

Uma nova área este ano no DAC é o Design Infrastructure Alley. A iniciativa da Aliança ESD e Associação para profissionais de computação de alto desempenho é uma área dedicada à infraestrutura de TI para o projeto de sistemas e componentes eletrônicos. Além dos requisitos de computação e armazenamento para projetar e gerenciar o uso da nuvem, há um pavilhão dedicado ao Design-on-the-Cloud que discute gerenciamento de licenças, computação em grade e segurança de dados.