Informações

O dsPIC recebe dois núcleos rápidos de 16 bits para acelerar o desenvolvimento de controle de potência e motor de alto desempenho

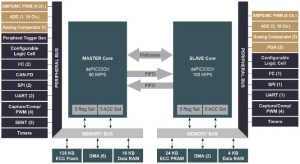

Com o objetivo de acelerar o desenvolvimento de código, removendo a dependência entre a interface do usuário e o código em tempo real, os núcleos são amplamente independentes, cada um com seu próprio conjunto de periféricos e se comunicando entre si apenas via FIFOs e caixas de correio. não compartilhado.

Dentro dsPIC33CHcomo a família será conhecida, os núcleos são semelhantes, com um funcionando a 90MHz designado como "mestre" e um "escravo" a 100MHz. O mestre tem mais interfaces seriais, enquanto o escravo tem mais ADCs, canais PWM e comparadores, por exemplo (veja o diagrama).

“O núcleo escravo é útil para executar código de controle dedicado e crítico, enquanto o núcleo mestre está ocupado executando a interface do usuário, monitoramento do sistema e funções de comunicação, personalizadas para o aplicativo final”, disse a empresa. “O dsPIC33CH foi projetado especificamente para facilitar o desenvolvimento de código independente para cada núcleo por equipes de projeto separadas e permite integração contínua quando eles são reunidos em um único chip.

As aplicações potenciais incluem energia digital e controle do motor, por exemplo, em energia sem fio, servidores, drones e sensores automotivos.

Em uma fonte de alimentação digital, de acordo com a Microchip, o núcleo escravo gerencia os algoritmos de matemática intensiva, enquanto o núcleo mestre gerencia de forma independente a pilha de protocolos do PMBus e fornece monitoramento do sistema. Em um ventilador ou bomba automotiva, o núcleo escravo gerenciaria controle de velocidade e torque com tempo crítico, enquanto o mestre gerencia a comunicação CAN-FD (taxa de dados flexível de CAN), o monitoramento e o diagnóstico do sistema.

As atualizações de firmware ao vivo ("zero tempo de inatividade") são possíveis em ambos os núcleos porque cada uma delas tem duas lojas de programas flash - quatro no total.

Se upgrades ao vivo não forem necessários, o dobro da quantidade de memória de programa disponível para o núcleo.

Comparado com a família dsPIC anterior destinada ao mesmo mercado - dsPIC33EP / GS - o desempenho é quase o dobro (latência abaixo de 543ns para 280ns) - parcialmente através da velocidade de clock de 70MHz para 100MHz e parcialmente através de: switching de contexto mais rápido (acumuladores contextuais) e registros de status) e novas instruções (divisão mais rápida, 32bit load / store).

Existem oito variantes de pacote, desde o 28pin dsPIC33CH64MP202 até 80 pinos e de 5 x 5mm para cima.

As opções de flash variam de 64 a 128 kbytes.

O suporte vem de:

- MPLAB X IDE

- Configurador de códigos

- Placa de Curiosidade dsPIC33CH (DM330028)

- Módulo plug-in dsPIC33CH para controle de motor (MA330039) para MCLV-2 e MCHV-2/3

- Módulo plug-in dsPIC33CH para plataformas de uso geral (MA330040) para Explorer 16/32 (DM240001-2)